AIC Review

思想和设计

一阶近似

忽略精确数值的计算,关注设计的大方向

将系统近似线性化

当考虑线性度的时候不能忽略Taylor展开的高阶项

PVT : Process Voltage Temp.

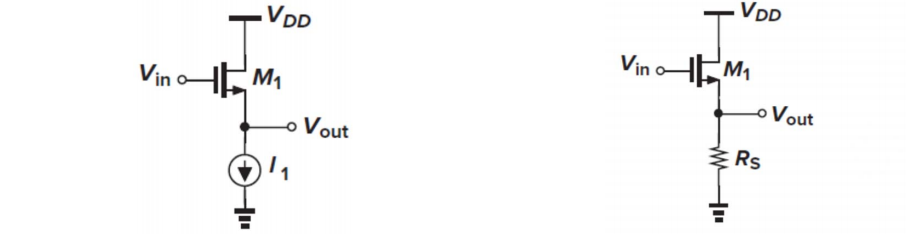

Current mode

- 将饱和区的MOSFET视作一个VCCS

- Norton 等效法分析线性系统

- Current mode technique

Current mode technique

- 找到的位置,建立各个管子和的联系

- 确定小信号通路,将Norton等效电流

- 计算effective transconductance

- 计算管子的output impedance 和load

传统设计步骤

-

分配各级电流 因为功耗很重要,一般先定

可以通过SR等确定电流下限

-

根据设计指标(PM、BW等)确定部分尺寸关系

-

估算,分配路径上的过驱动电压

先进工艺往往采用法设计

-

确定

-

确定偏置 首先确定一个reference current,然后利用current mirror产生bias current or voltage

-

检验是否处于饱和区

大信号分析

管子所处的工作状态(DC Bias)

一般管子要求处于饱和区:有利于大的增益

- 作放大:大的

- 作loading(current source):大的输出阻抗(大电阻)

input/output range: 限制条件即每个管子都工作在正确区域

显然: 设计追求更大的headroom

管子工作在线性区

- 一个可调的小电阻

- 电容(not linear but cheap)

小信号分析

线性方法、近似 计算具体的放大性能参数

- 确定每个管子的DC Bias

- 求得每个管子的

- 作出小信号电路

- Common ground

- 小信号模型: 适时忽略部分

- 应用线性系统分析方法计算参数

信号表示

- 大写表示DC Bias,如

- 小写表示小信号,如

- 混写表示全部信号,如

负反馈

-

高阻抗点的电压要在close loop中定义

差模和共模要分别用负反馈定义

因为差模仅看到差别部分,共模仅看到相同部分

(如两点电压一起抬升超出range无法被差模负反馈抑制)

-

控制某个node电压,boosting

Device

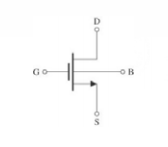

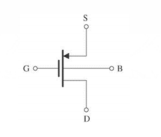

Symbolic representation

-

n-MOSFET

-

p-MOSFET

Cut off region(类switch)

- =0

Sub-threshold region

- 低功耗设计

- 近似模拟BJT:因为I-V曲线类似,都是e的幂指数形式

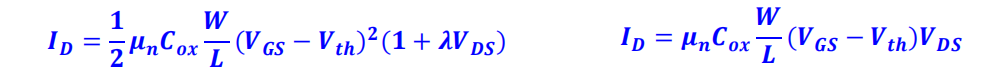

Linear region(类resistor)

- :当较小时忽略二次项

- 含义:近似为一个电阻

Saturation region(类current source)

-

-

:沟道调制系数,随着的增加而下降

在长沟道较准确

-

含义:近似为一个稳定电流源,输出电流由

逍遥二仙

非理想效应

-

Body effect 衬底(Substrate/Bulk)电压非零

上升

-

Shot-channel effect

略

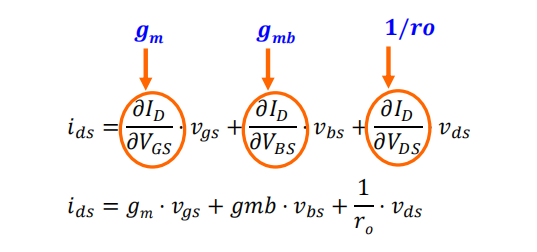

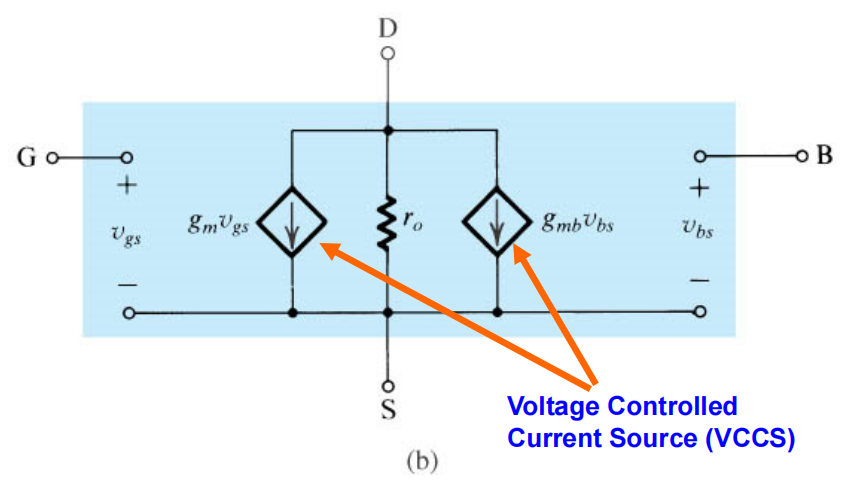

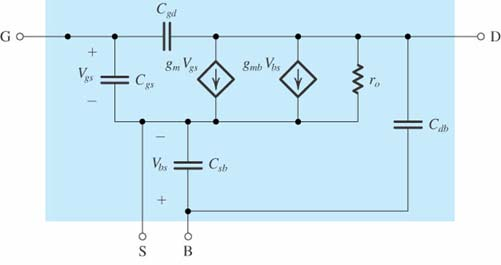

小信号模型

昆仑三圣

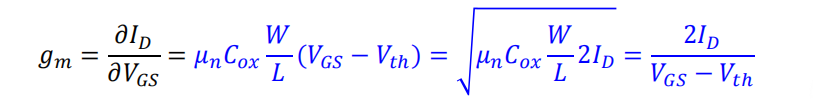

transconductance

-

直接影响gain、speed

-

饱和区最大

-

亚阈值区(transconductance efficiency)最大

weak inversion region for low power consumption design

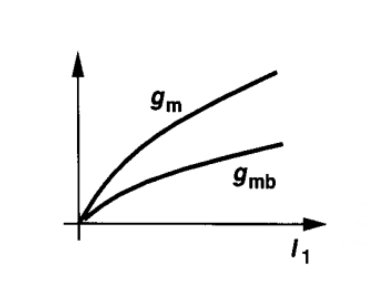

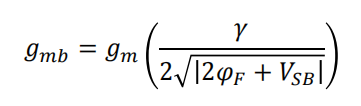

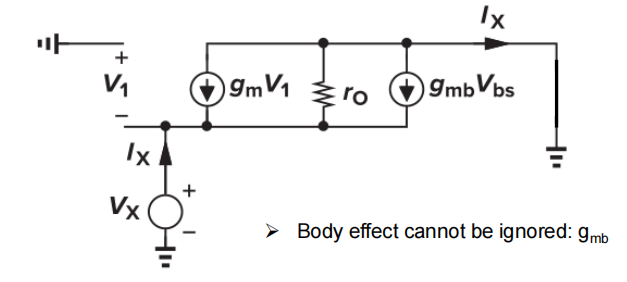

Bulk transconductance

-

利用代价较大

-

效率不如高,常常用作帮助,大致为10%~20%的

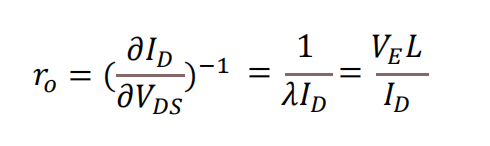

Output transconductance/resistance

-

一般很大,有时候分析可以视该支路作开路

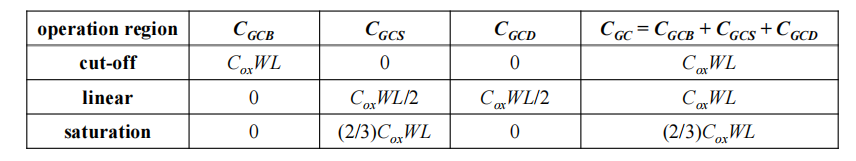

小信号模型(电容版)

分析频率响应时候引入,即低频可以忽略,高频率不可

unity current gain frequency 电流增益为1

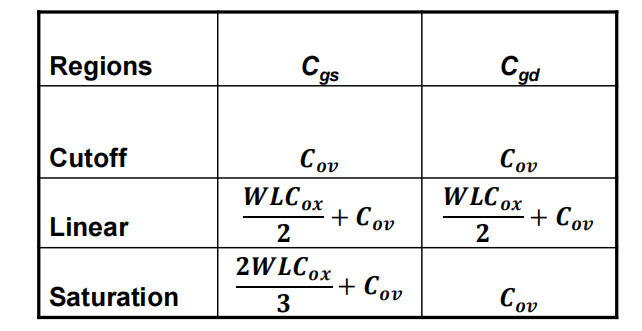

多种电容

-

Overlap Capacitance 覆盖电容

由于工艺原因部分source/drain延申到Gate下方形成电容

-

Gate-to-Channel Capacitance 栅至沟道电容

-

diffusion(junction) Capacitance扩散电容(节电容)

扩散区处于反向偏置的源体、漏体间的p-n结引起的电容

电容综合

-

-

-

-

-

$C_{GB}=C_{GCB} $ 线性区、饱和区为0

未必增加: trade off

Single-Stage Amplifier

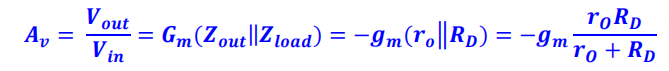

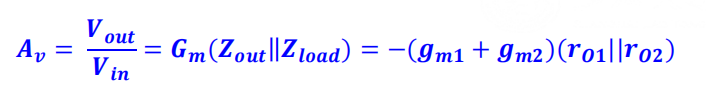

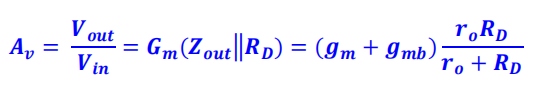

Voltage gain:

Current gain:

Power gain:

本质:amplifier将DC power 转换为small signal power

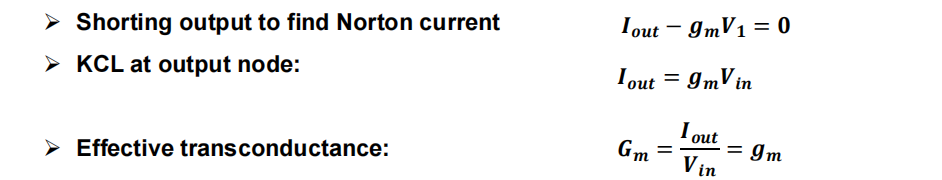

Current mode technique

-

找到的位置,建立各个管子和的联系

-

将Norton等效电流

-

计算effective transconductance

-

计算管子的output impedance & load

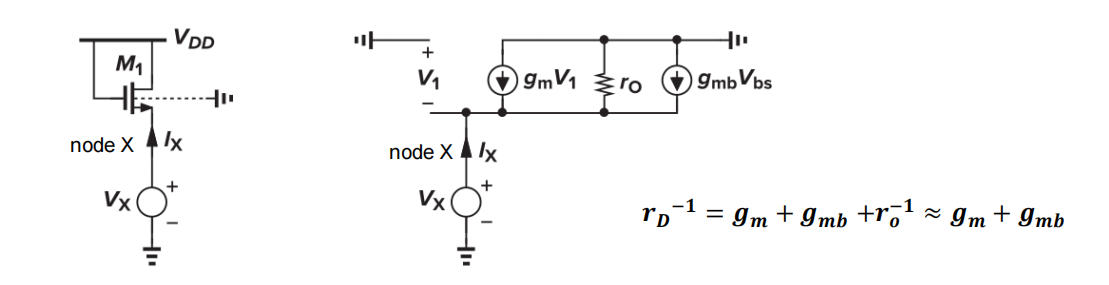

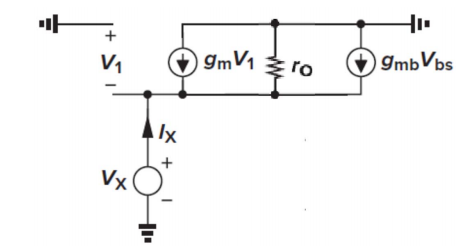

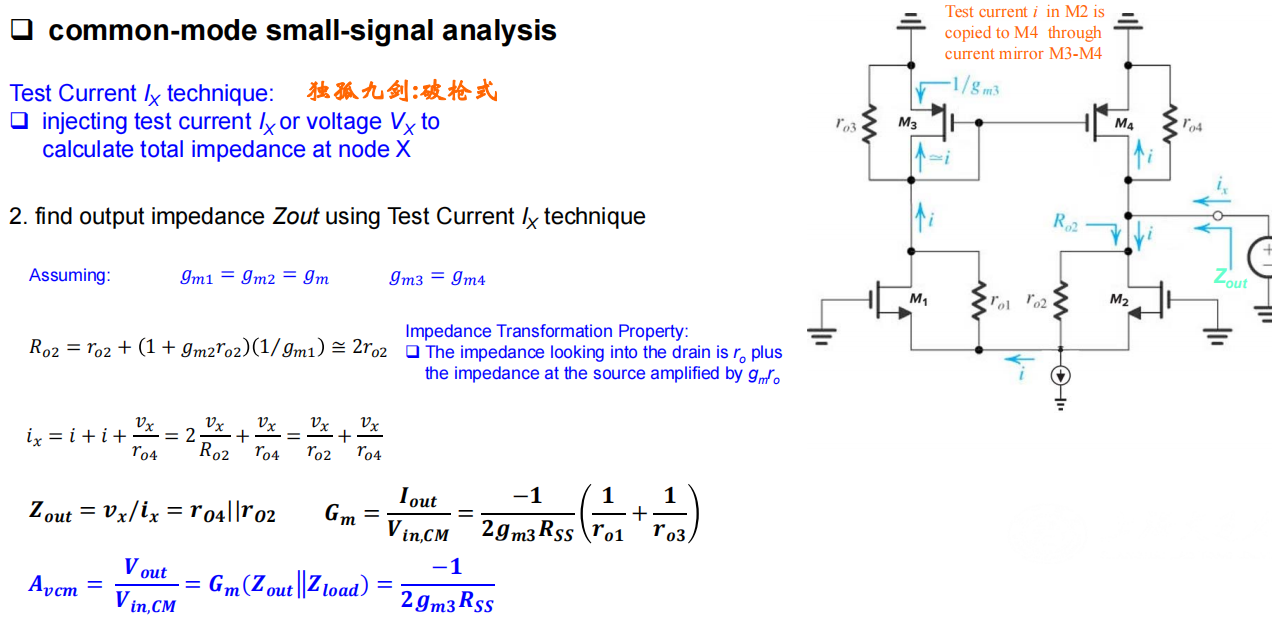

采用test current technique

-

Test current technique

计算node X处的阻抗

-

在node X处插入test current 、Test Voltage

其余独立电源置0(戴维南等效电阻:等于有源二端网络内所有独立电源置零(独立电压源短路,独立电流源开路) 时,得到无源二端电路N的端口等效电阻)

-

各点阻抗的重要性:根据其数值量级大小对带宽bandwidth的影响不同

存在多级别:

需要一眼定位其重要性!!!

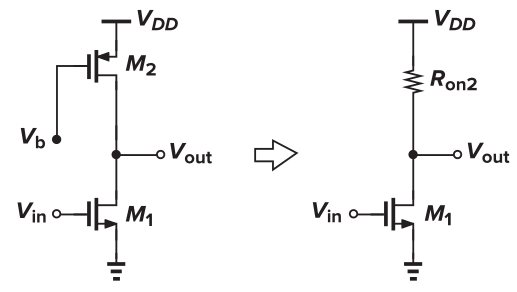

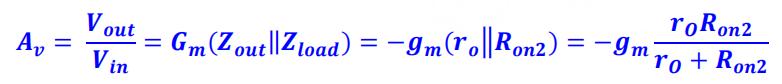

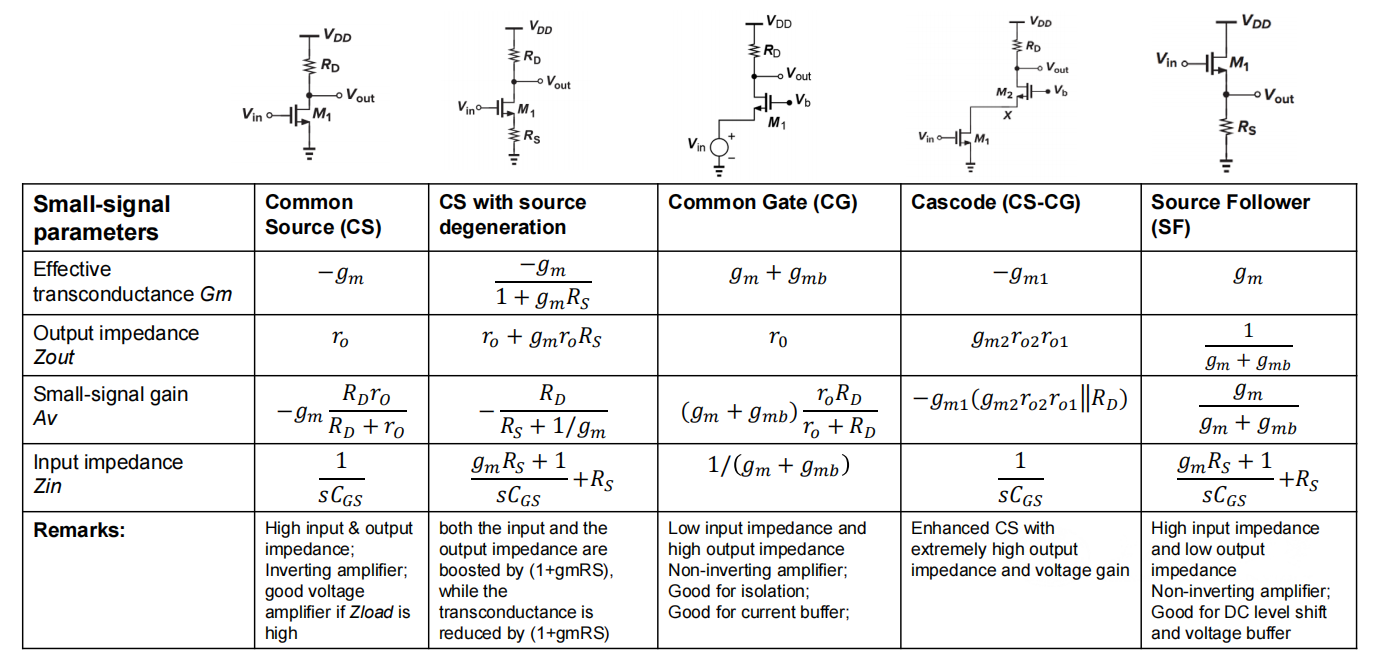

Common Source

输入在gate端,输出在drain端:source作为common reference

DC bias:保证处于饱和区工作

current source/ resistor :bias up MOSFET,also serving as a load

1.resistor

当最大,即极限voltage gain为

想要增加

长沟道 一阶近似 无穷大假设下

-

增加WL

-

减少:与常识相反!!!

代价:更大的电容、面积;更大的时间常数、更慢的速度

2.linear region MOSFET

即 利用线性区类电阻

由于

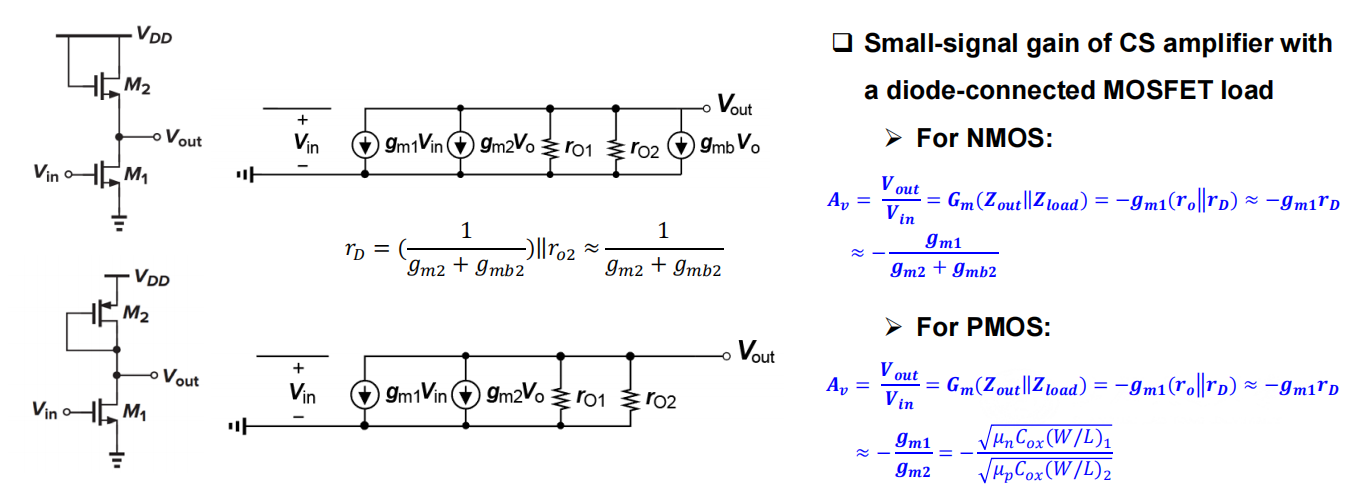

3.diode-connected MOSFET

该连接方法确保loading 管子处于saturation region

详细计算过程(以n-MOSFET为例):

-

将, Norton等效电流为-

-

放大管output impedance:

-

只需计算(test current tech.)

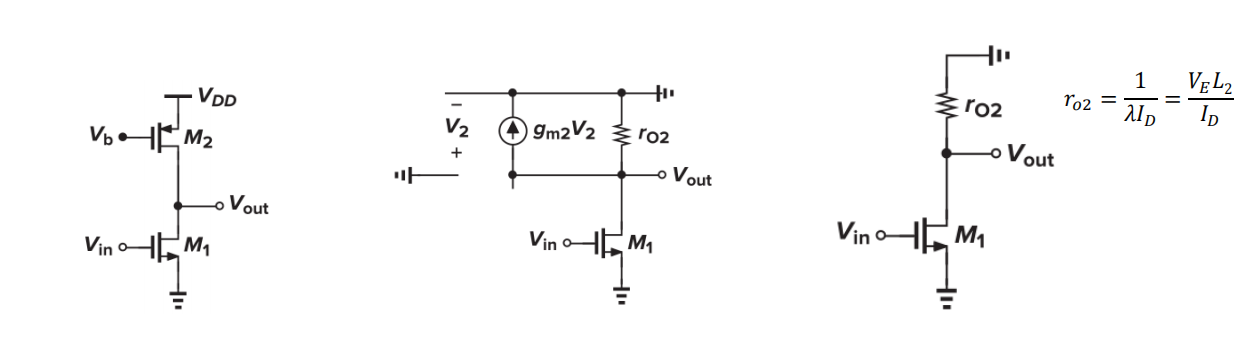

4.current source

理想的current source情况即

用saturation region的MOSFET类current source:

此时的 !!!

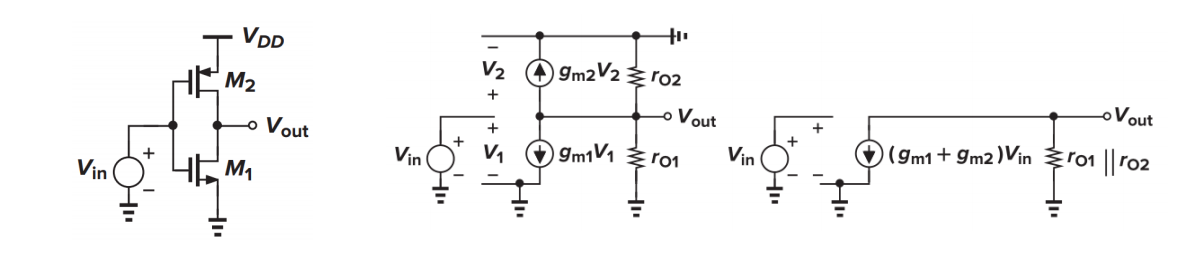

5.stacked CS amplifier(current reuse)

对上述进行改进,用同时偏置放大管子和load管子,即DIC中的inverter

此时几乎可以达到理想!!!

but: PVT problem!

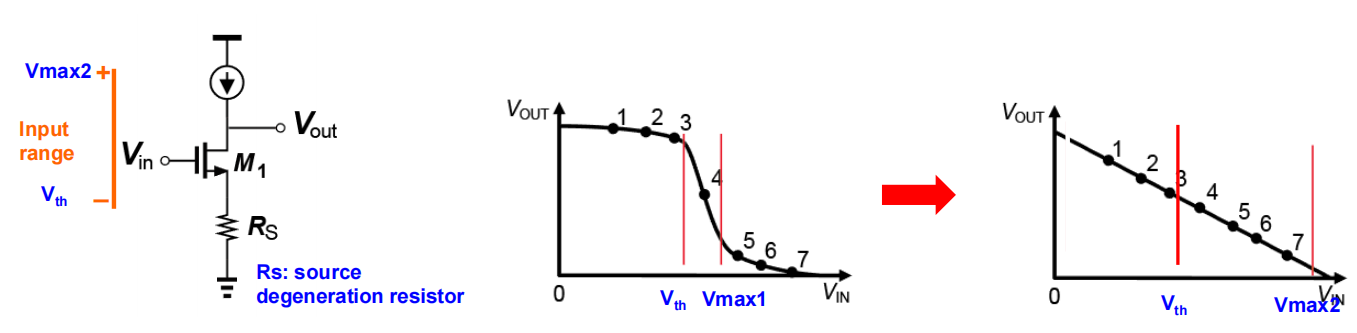

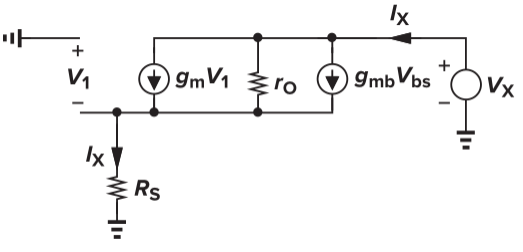

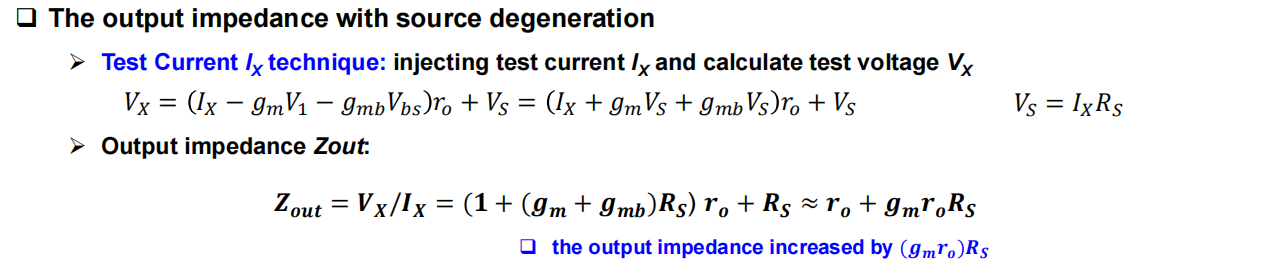

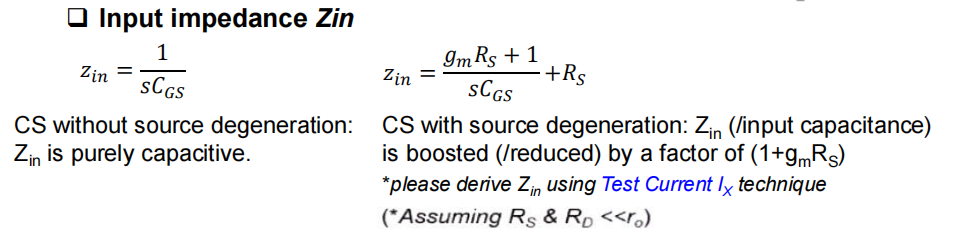

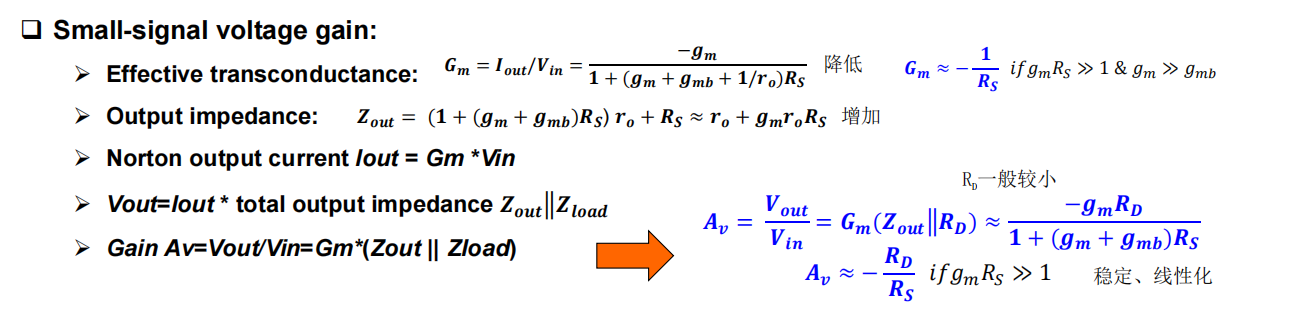

6. CS amplifier with Source degeneration

一般的: 定义为在common source上加上任何阻抗

常见的: 定义为在common source上加上resistor (形成负反馈!!!)

- 改善input range,拉长线性范围

- 改善input/output impedance

- 代价是减少了

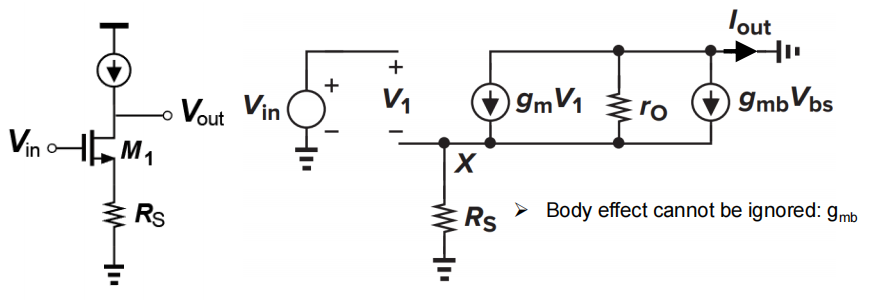

详细计算过程:

1.

2.

3.

Assuming: ,if not:

-

若

小信号模型中 -

若

小信号模型中视作断路,形成一个小的内循环

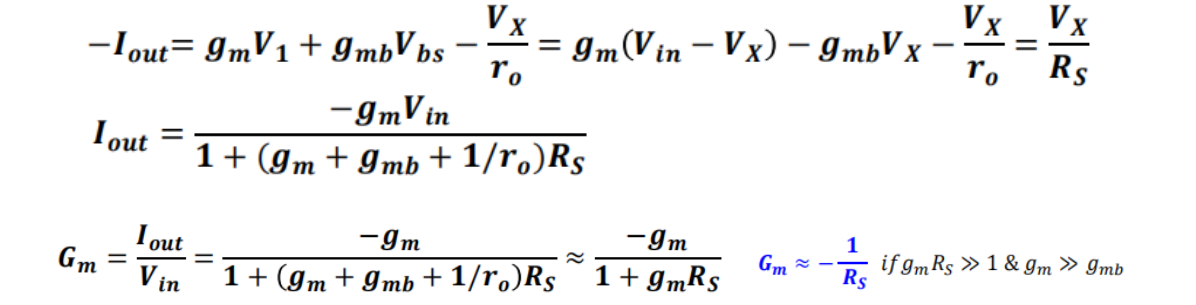

4. summary

Impedance Transformation Property (MOSFET in Saturation)

可以大致判断阻抗大小级别, 会存在一点误差(如等)

-

The impedance looking into the drain is plus the impedance at the source amplified by

drain看, 高阻抗: 乘了 至少级

-

The impedance looking into the source is plus the impedance at the drain attenuated by

source看, 低阻抗 :除了 一般级

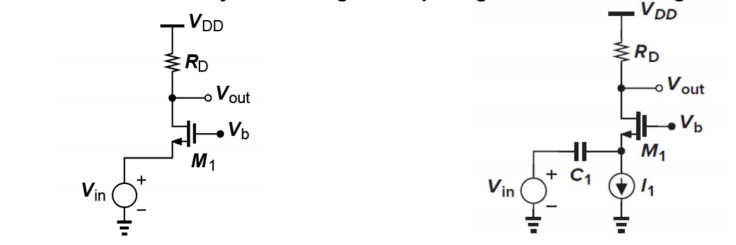

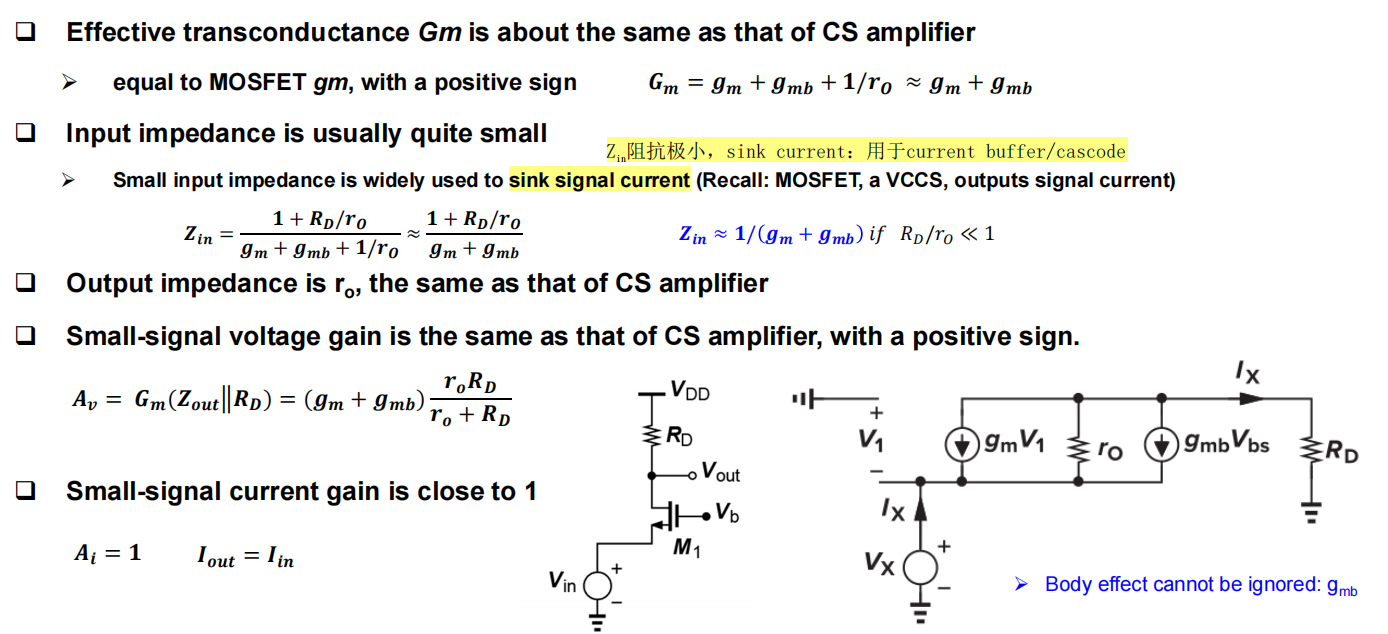

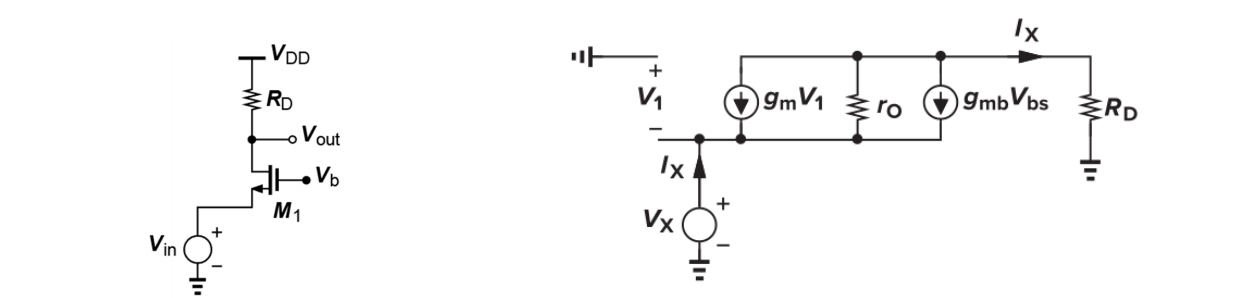

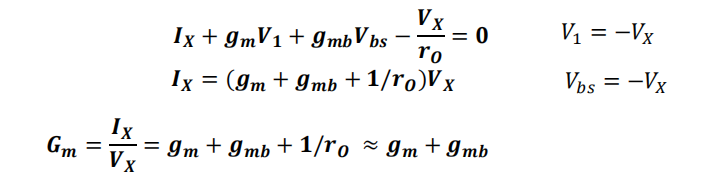

Common Gate

输入在source端,输出在drain端:gate作为common reference

详细计算过程:

1.

和common source 大小一样,仅符号相反:导致

2.

3.

符合阻抗转换定则:约等于

极小的输入阻抗,用于sink current

配合较大的输出阻抗,可以起到很好的隔离作用

4.

current gain为1:current buffer!!!

作隔离:极小的输入阻抗 ,约为

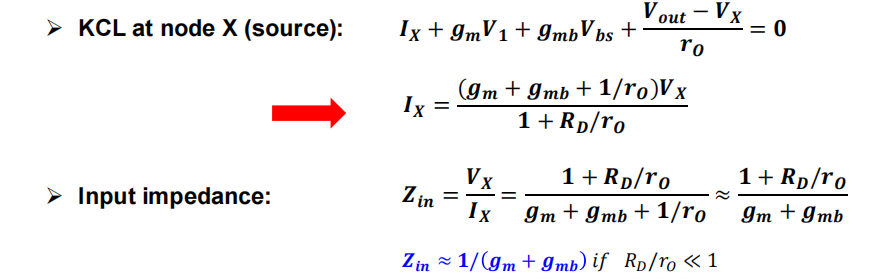

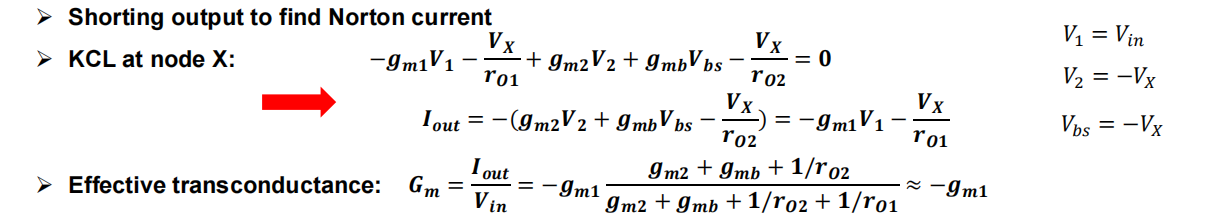

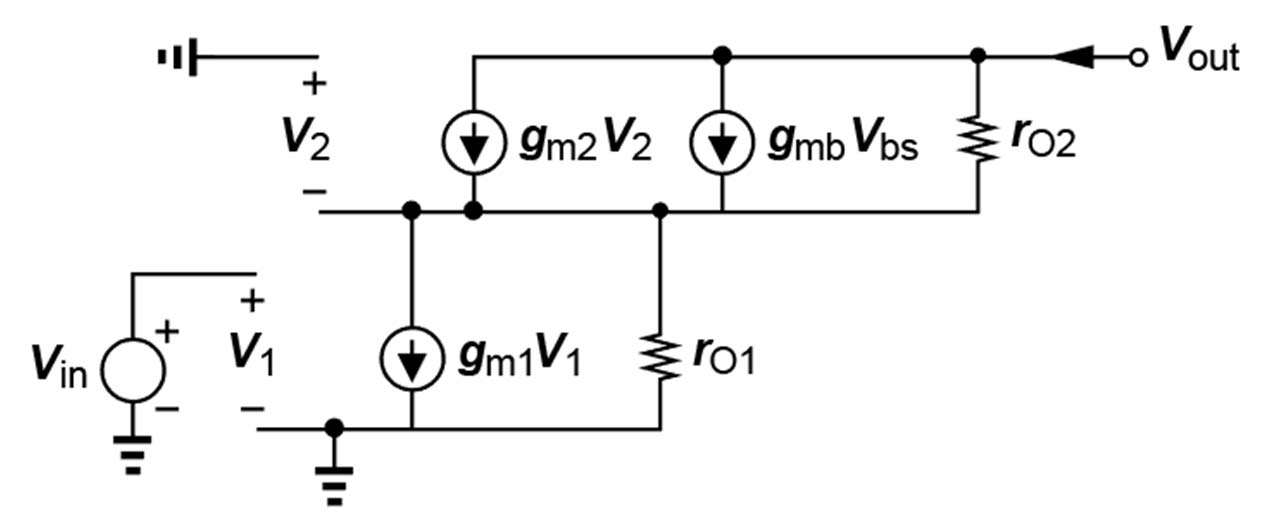

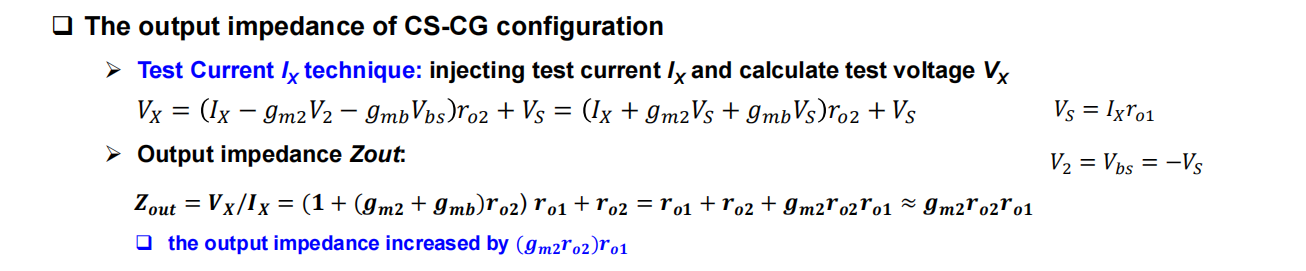

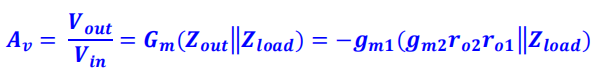

Cascode: CS-CG configuration

- CS: 实现放大

- CG: sink current (current buffer)&增大output impedance by *

- reduce Miller effect by /

- 好的控制能力:

but: voltage headroom problem

详细计算过程:

1.

2.

输出阻抗被极大放大

和阻抗转换定则一致

:可以采用cascode current source作load

3.DC analysis

Voltage headroom problem

保证CS、CG MOSFET都工作在saturation region

input、output range

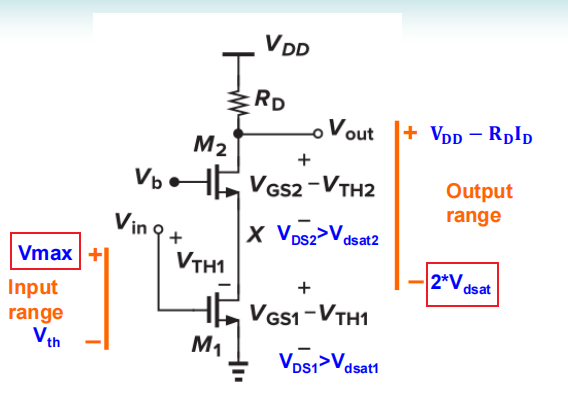

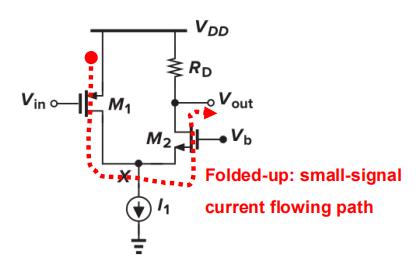

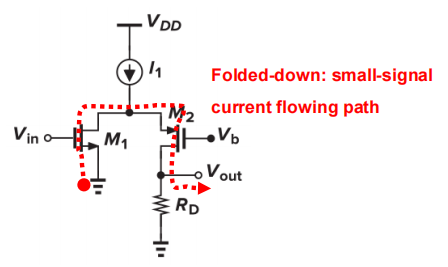

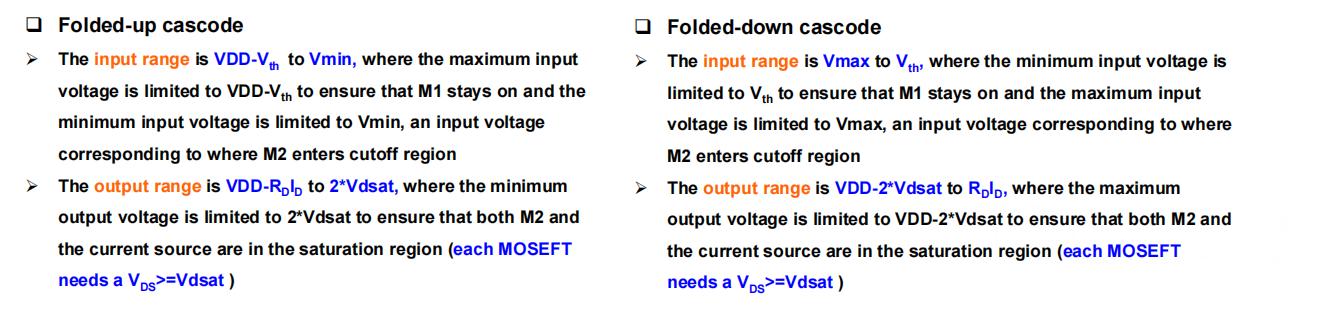

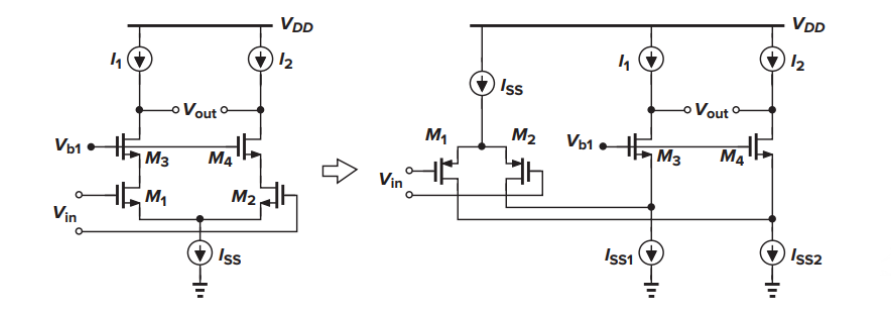

4.Folded Cascode

current mode 思考

-

folded-up:

-

folded-down:

对普通cascode的input、output range进行了一定平移

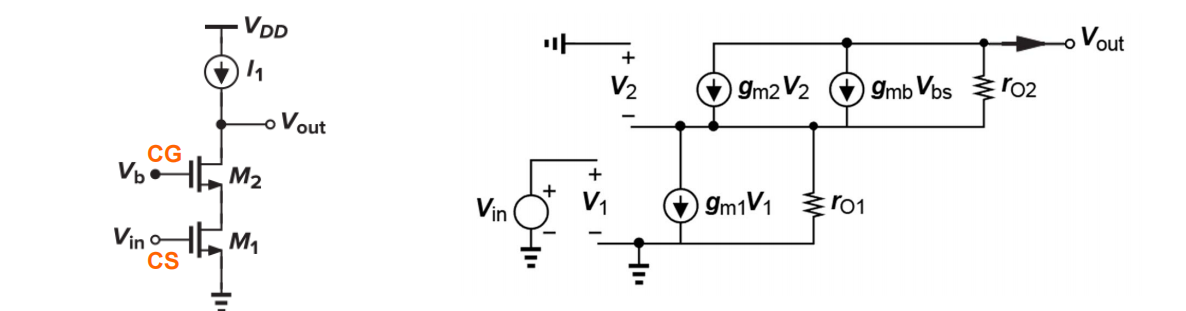

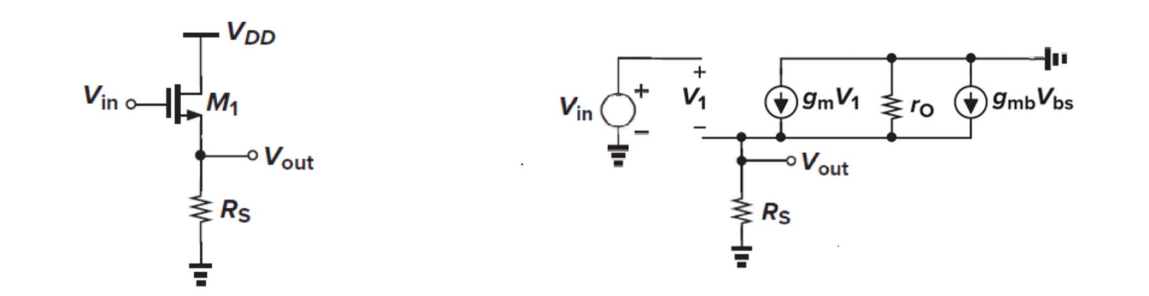

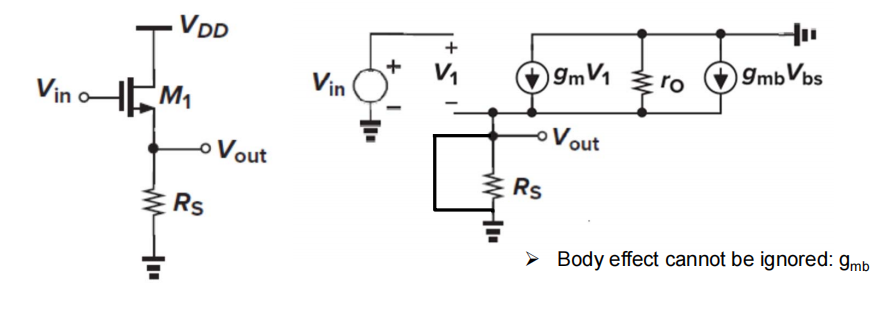

Common Drain (Source Follower)

历史原因:Source Follower 更有名

输入在gate端,输出在source端:drain作为common reference

current source/ resistor :bias up MOSFET,also serving as a load

详细计算过程:

1.

和common source 大小一样,仅符号相反:导致

2.

极小的输出阻抗

“Follower” : source voltage will follow

消除Body effect

更接近1

- 采用p-MOSFET

- twin-well 工艺

作隔离&高功率driver

- 低输出阻抗、高输入阻抗:好的voltage buffer

- 前一级无法提供后一级所需的大电流:加入SF,保持电压&提供电流

Summary

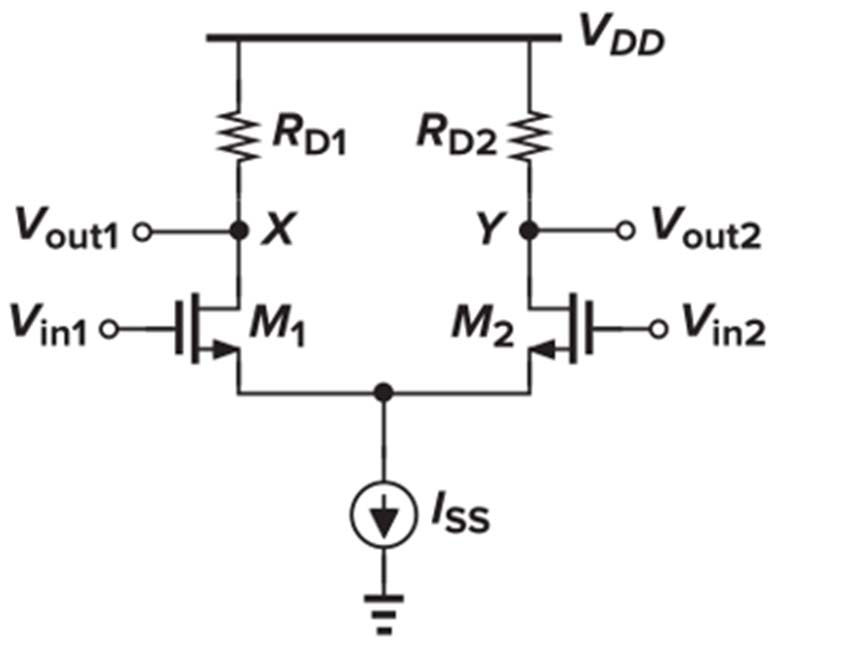

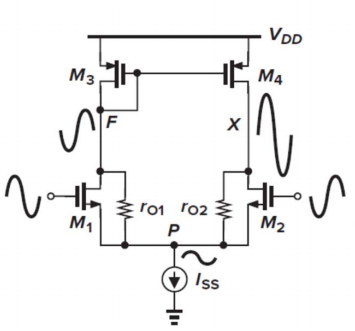

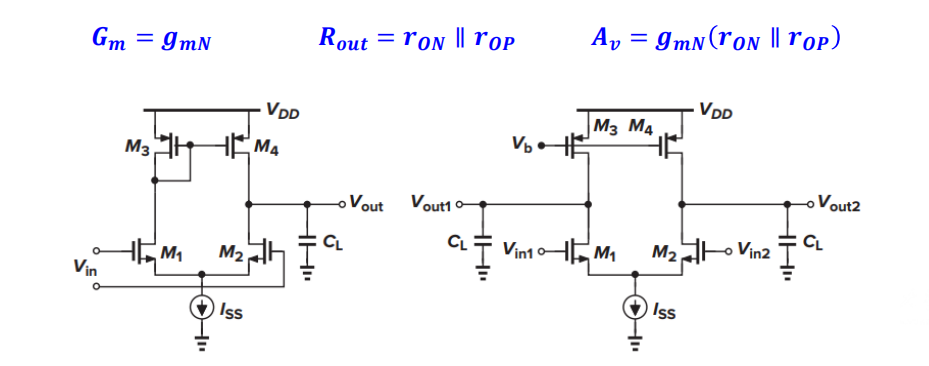

Differential Amplifiers

Single-ended vs Differential amplifier

-

Single-ended amplifier

- cheap(远程传输)

- widely used(大部分Amplifier的输入输出模式)

-

Differential amplifier

处理信号,抵抗common mode

对环境噪声和电路干扰(power supply,串扰,ground等)不敏感

inputs:

- Common Mode signals:, 作reference voltage

- Differential Mode signals:, 储存信息

outputs:

-

-

Fully differential:

若信号尚未处理完毕,存在下一级的differential inputs接收端

信号传输用单端, 处理用差分

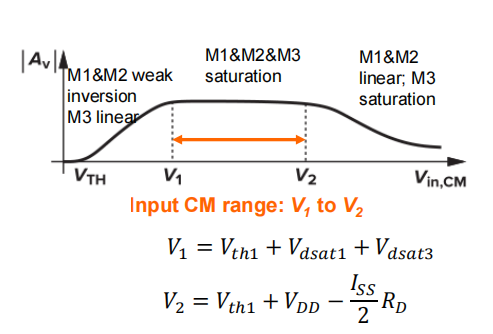

Requirement&Analysis

-

matched/balanced signal paths for two inputs

差模输入信号:在输出端差分,因为极性相反doubled

共模输入信号:在输出端差分,因为极性相同消去

Offset Voltage: mismatch产生,基本都是不利的

-

common-mode gain<<diff-mode gain

common mode 影响到bias

若common-mode gain很大,可能会使得管子离开饱和区,产生失真/非线性

-

对common-mode&diff-mode signals都需进行大信号分析和小信号计算

Half circuit technique

-

将输入信号分为共模和差模部分

linear system only!

-

将amplifier电路沿中心对称轴分为两半,计算half circuit的

if well matched: diff-mode中心轴上电路电压不变,视作virtual ground

-

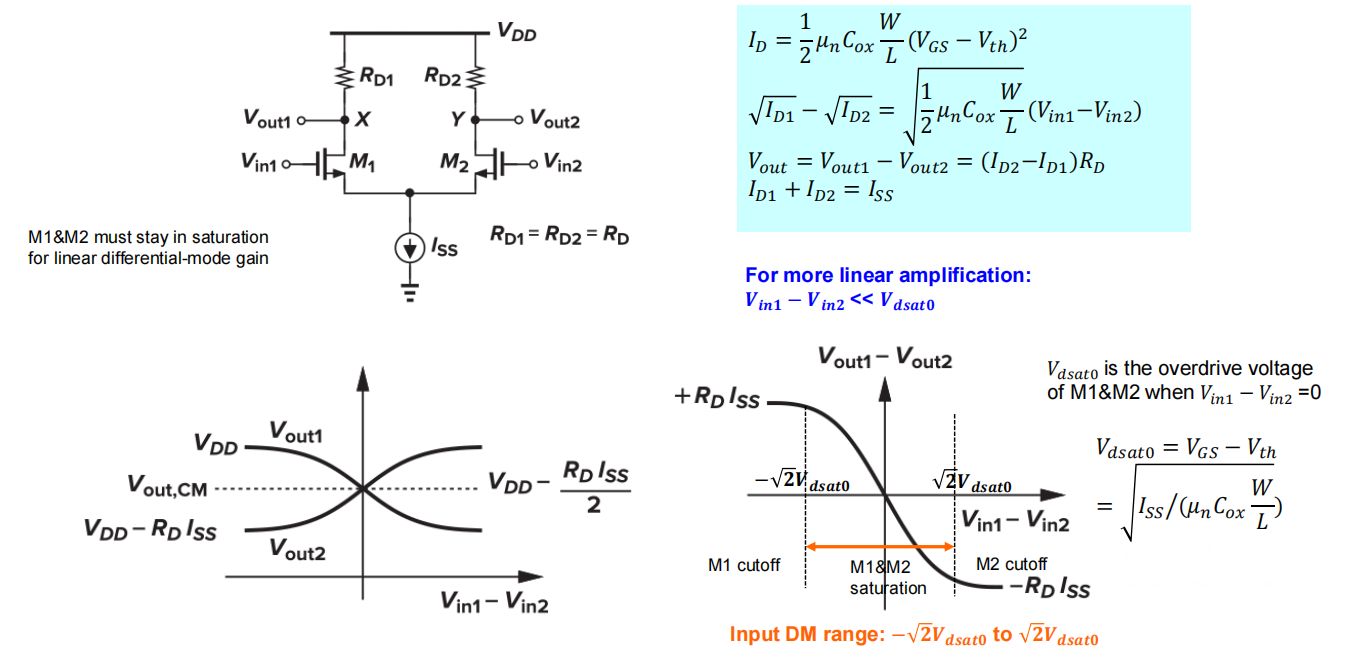

Diff Pair

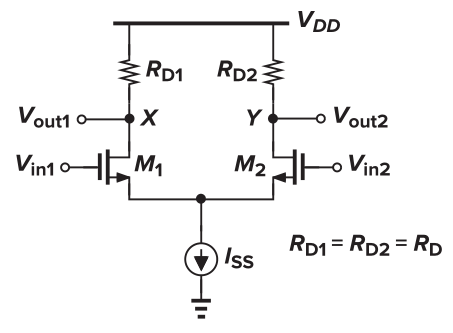

conventional structure

两个对称的common source amplifier,一个tail current source

tail current source作为source degeneration:

只对common-mode有效,且因为 极大而有效抑制了common-mode gain

diff-mode为virtual ground,不对diff-mode gain 产生影响。

but: voltage headroom problem&noise from tail current source

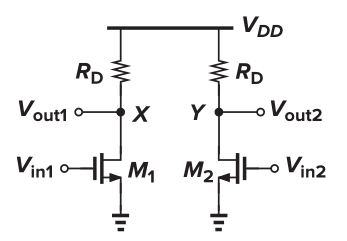

Pseudo differential pair

去除tail current source,解决了上述问题:

but: no common-mode source degeneration

过高的CM gain可能导致small input range problem

电流纯粹为 input-dependent,失去了tai current source的上限限制

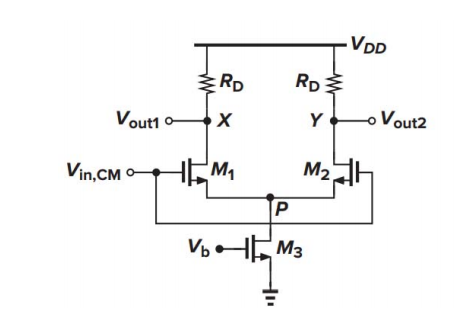

Large signal analysis

1. Common mode

input common mode 的dc part作为放大MOSFET管子的dc bias

2.Diff mode

差分输入的信号不能过大,会让放大mosfets管子不在饱和区工作&影响线性度

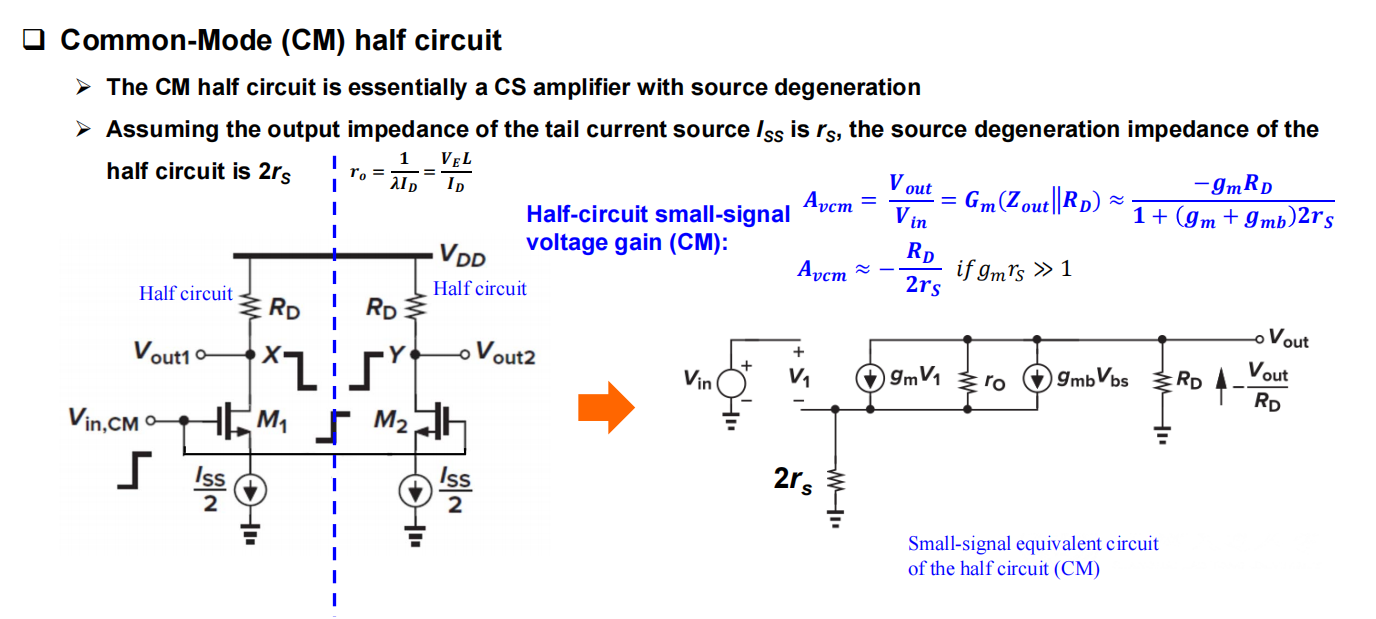

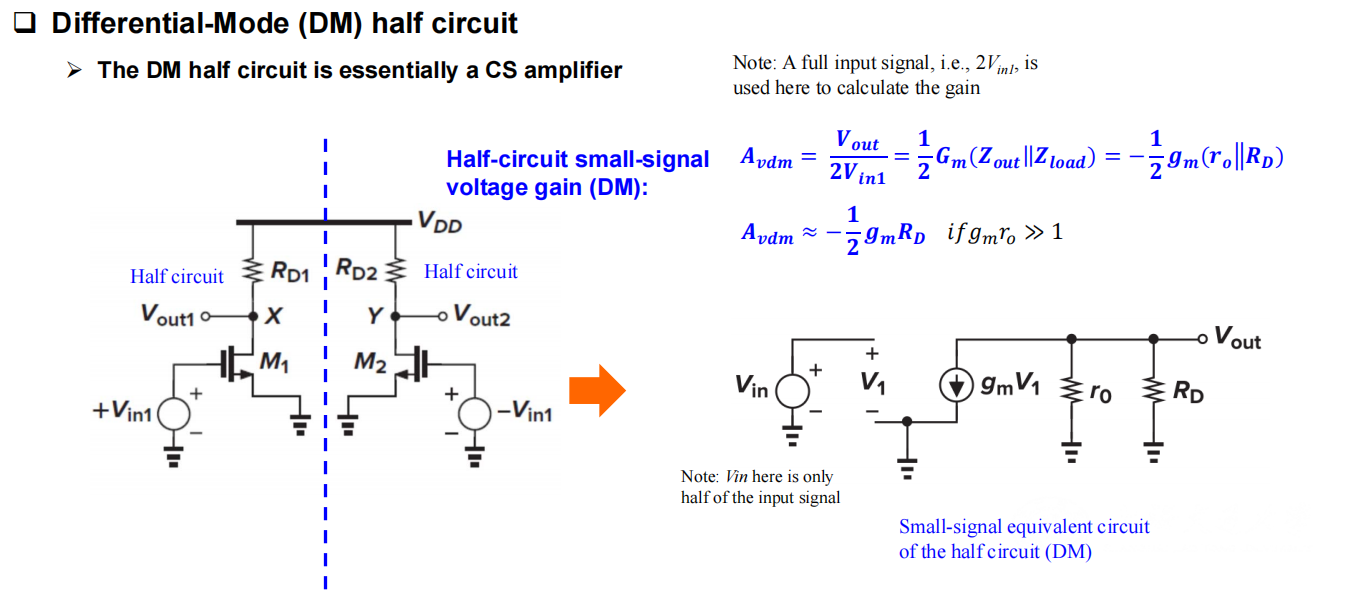

Small signal analysis

half circuit technique¤t mode technique

half circuit各自分析时即为common source single-ended amplifier

1.Common mode

tail current source拆做两个并联,之后各自分析即可

2. Diff mode

两边输入极性相反,一边上升一边下降,中间对称轴上电压不变,视作virtual ground

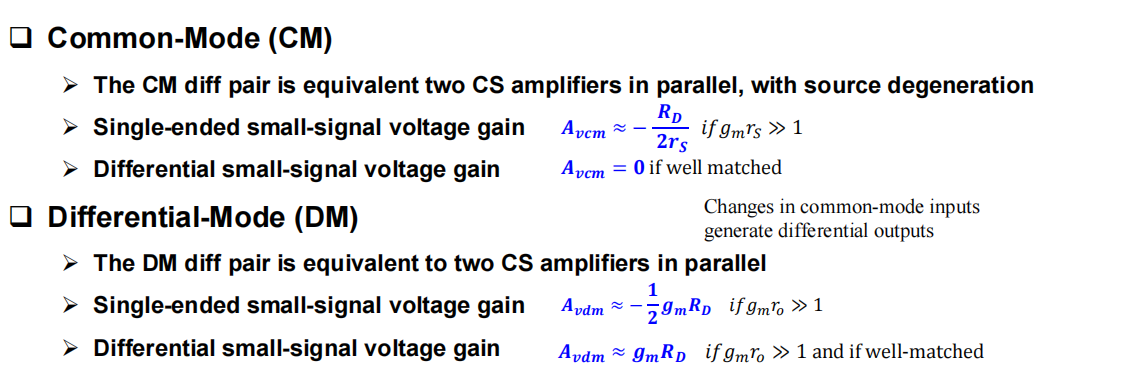

3.Summary

-

common-mode:

-

diff-mode:

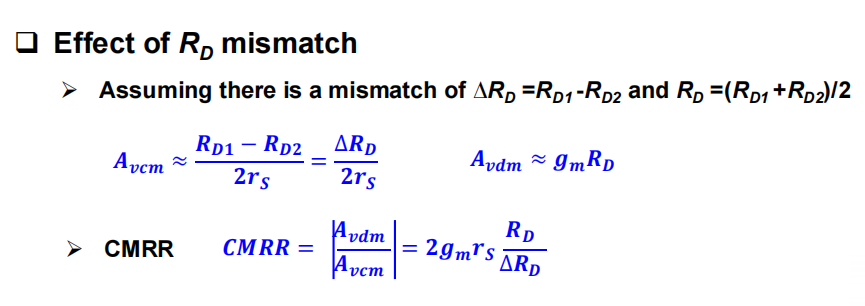

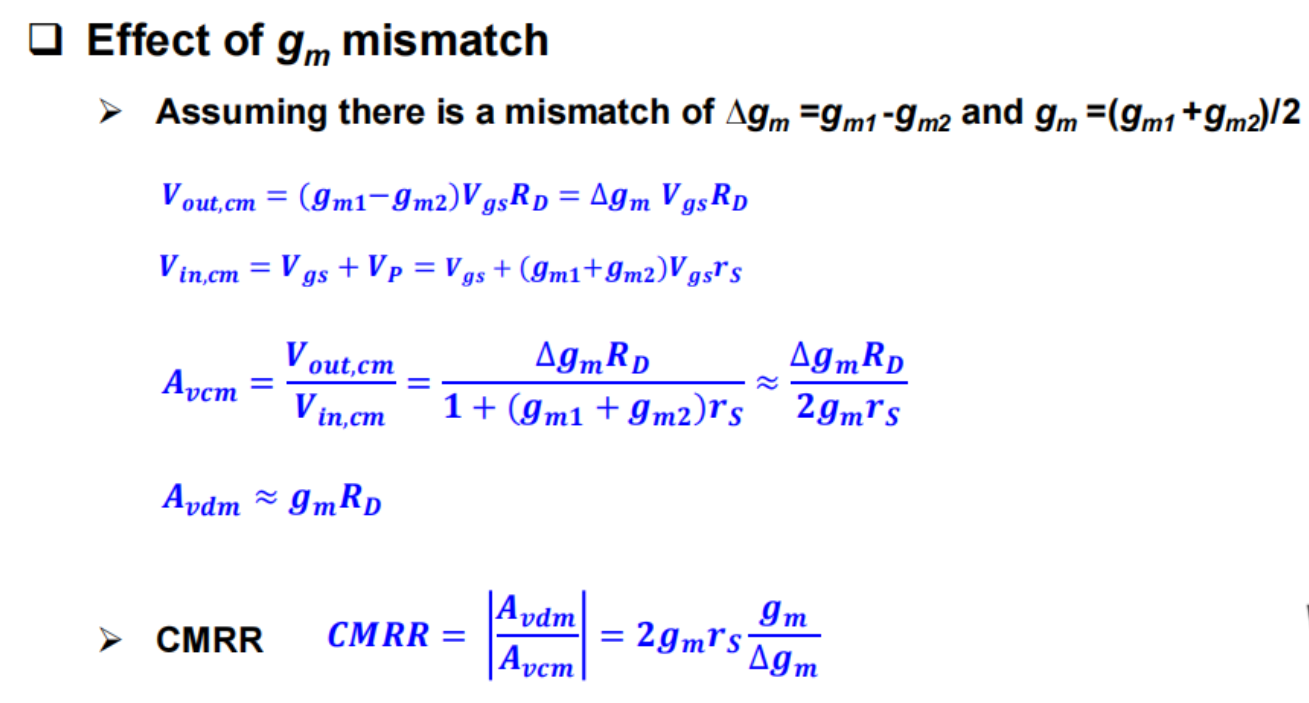

CMRR

描述了抑制共模噪声的能力

和信噪失真比SNDR息息相关

理想的:

- single-ended:

- differential:

Mismatch for CMRR

各种mismatch使得CMRR不等于∞

可以利用小信号分析的single-ended公式近似计算不同情况CMRR

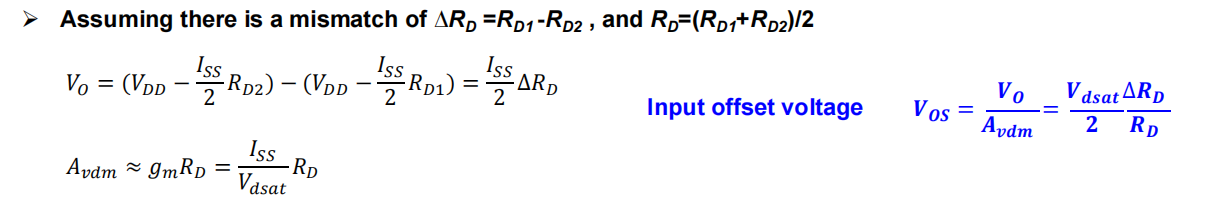

1. mismatch

2. mismatch

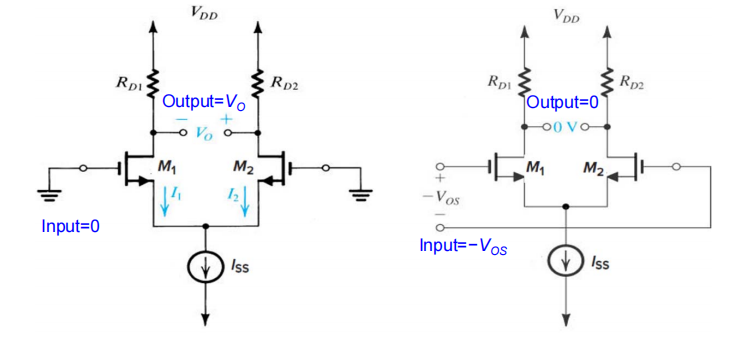

Offset Voltage

一个虚拟的input dc电压,抵消各种因素引起的当输入信号为0(diff-mode)输出非0

可以计算出从而计算

-

systematic offset voltage:电路设计产生mismatch

确定的,容易去除

-

random offset voltage: 随机产生的mismatch(生产等)

不确定,但有抑制的设计方法

去除offset的必要性:offset voltage相对input信号数量级更大(100倍)

1. mismatch

2. mismatch

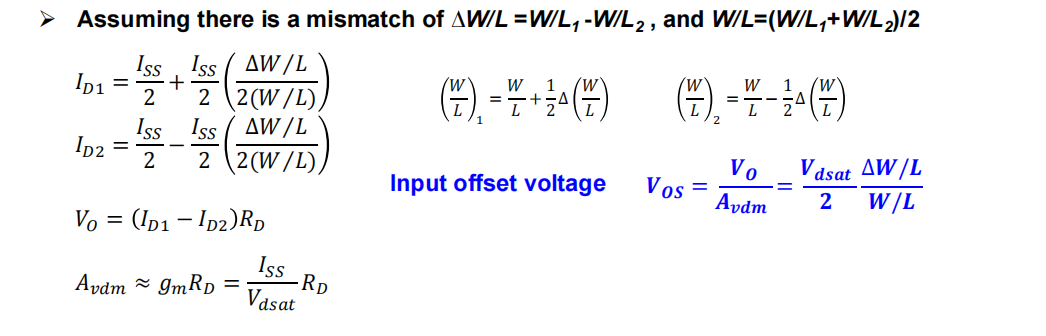

3. mismatch

4.total offset voltage

random offset voltage,由于互相无关:

对于给定

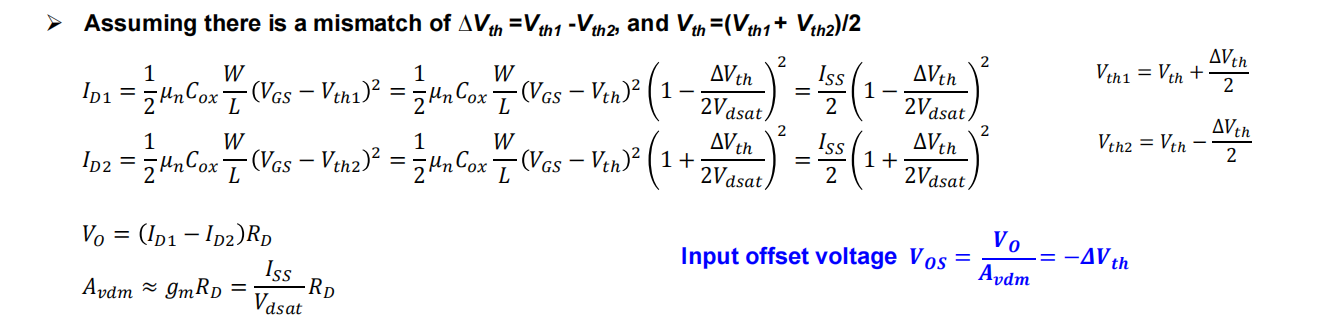

Active Load

why

-

为了较高的

-

用两个common source amplifier所搭的diff-pair无法实现single-ended output

可以只取一个端口作output:

but:增益损失6db(一半)、损失common-mode signal rejection(致命的!!! )

改进:利用current copier

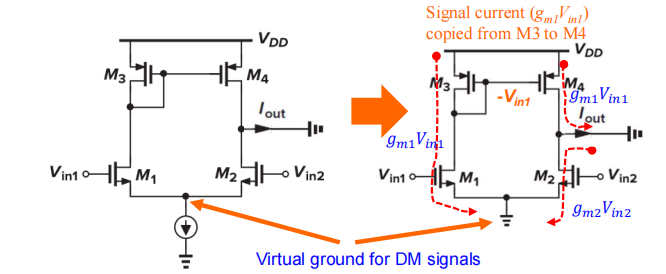

current copier

将左侧的input signal copy到右侧,即,从而实现差分

but:因为电路设计的mismatch:存在systematic offset voltage

进而导致了即使器件match,CMRR仍有限

high DC impedance node

大阻抗的node在电路设计中需要格外在意!!!

-

格外敏感:任何小的current signal都会因高阻抗被格外放大

电路极易饱和

-

决定了频率响应中的dominant poles

-

电压不确定:任何mismatch都会引发电压极大变化,使偏离设计的预想电压

需要用负反馈回路控制

-

必然存在:虽然不好,但因为需要大的增益,大阻抗node必然存在

single-stage amplifier一般为output node

以此时为例:output node向上看阻抗是,

而对侧node向上看阻抗仅)

small signal analysis

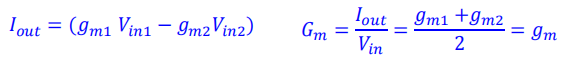

1.differential mode

-

计算

无法采用half circuit technique,因为不对称

-

计算

虚地不成立,因为电路单端,小信号是从output单端输入的

-

往上看:

-

往下看:CS with source degeneration,

-

寻求的关系:

为向下电流,绕一圈然后向上又copy一份

为另一个向上电流

问题:为什么不能直接向上看&向下看并联等效?

结果恰好和虚地的时候一致,但是是巧合!!!

-

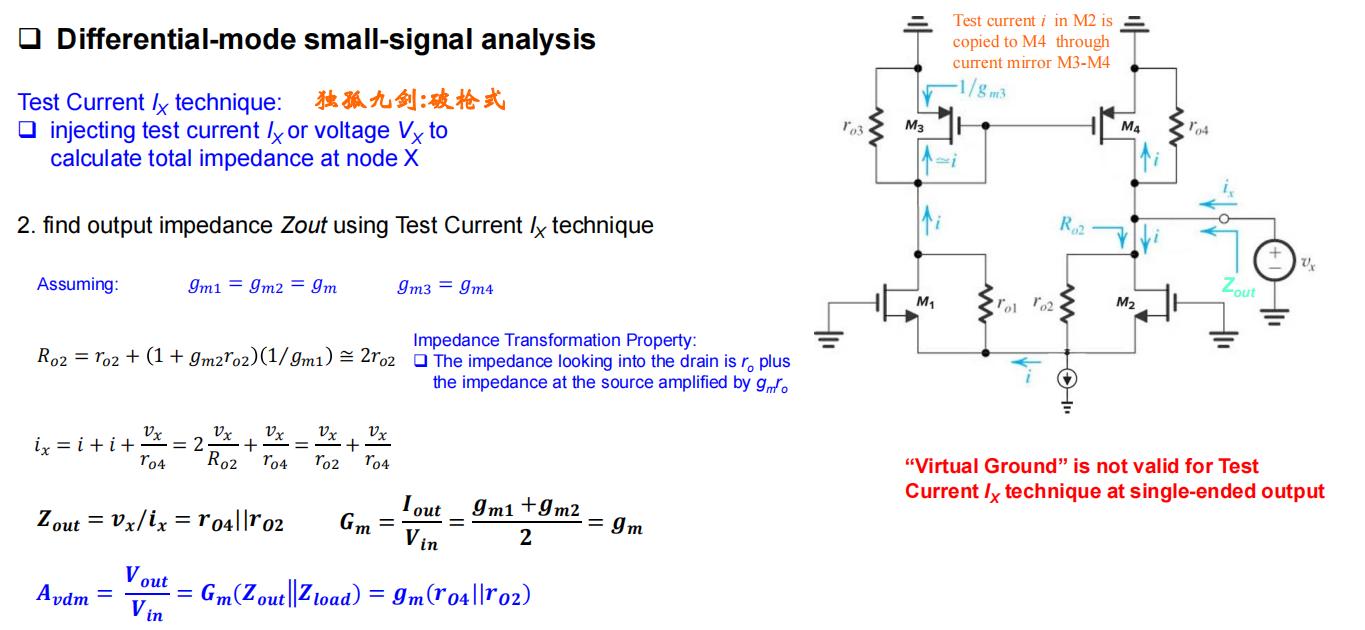

2.common mode

有效计算

输出阻抗和diff mode一致

3. CMRR

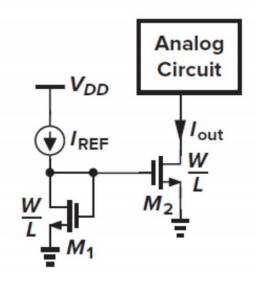

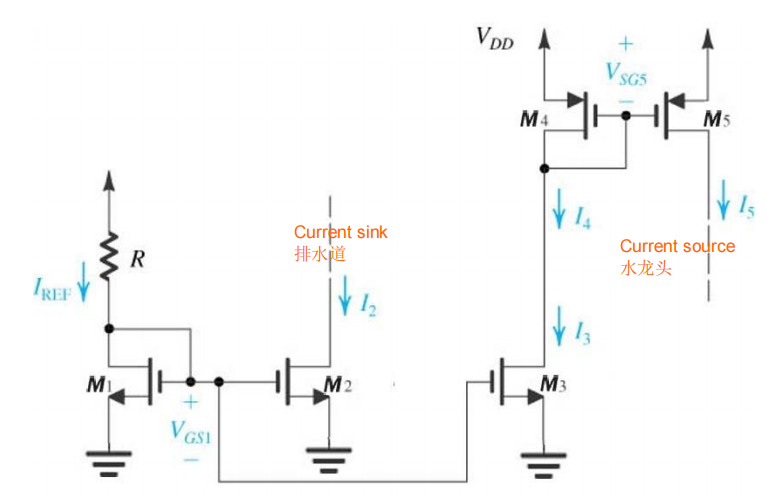

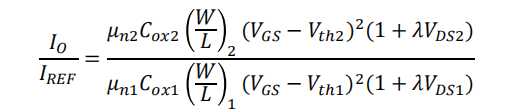

Current Mirrors

Current Source

最简单的current source :MOSFETs in saturation region

usage

- biasing for circuits:用电流源电流作其他电路偏置可以增强电路的鲁棒性

- high output impedance:电流源作loading,大增益

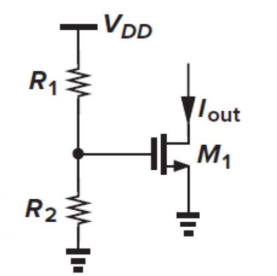

biasing for current source

- bad bias

but:极容易受到PVT影响&噪声性能差!!!

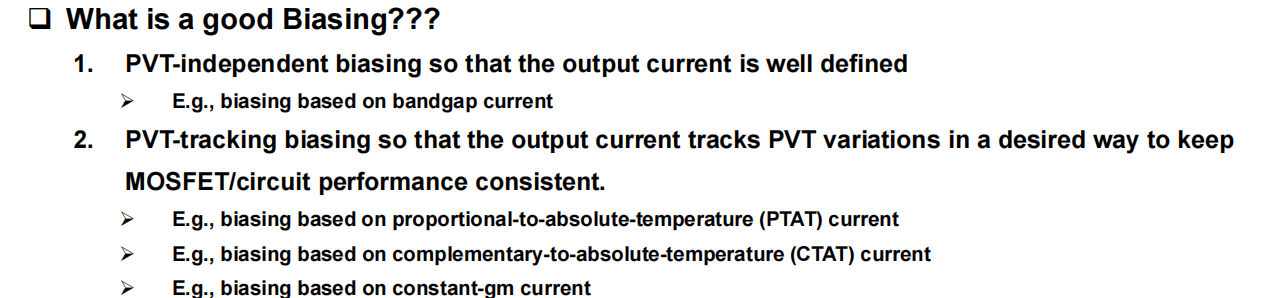

- good bias

PVT independent or PVT tracking(PVT 的变化使电路参数向好的方向变化)

bandgap current source:恒定电流

constant-gm current source:利用PVT使得gm恒定

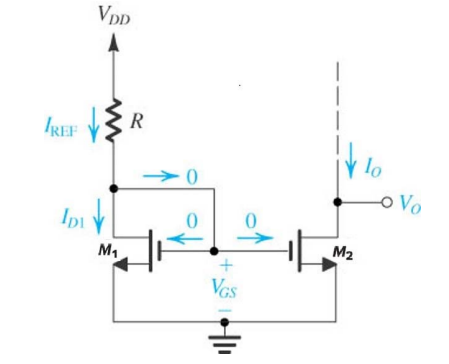

Current Mirrors/Copiers

用unit size的MOSFETs组成MOSFETs,放大其数目,相互耦合减少PVT影响

usage

-

将系统的 copy 出来作部分电路的current source&biasing

被copy电流为reference current:一般有 bandgap/PTAT/CTAT current等类型

-

信号传输&放大

被copy电流为signal current(例如diff-amplifier中的current mirror)

-

电流转向/改变大小:sink/source current &

requirements

-

high output impedance

1.long channel length:

2.boost output impedance : cascode configuration e.g.

-

well matching between MOSFETS

Ensure both MOSFETs see the same

1.using tracking/feedback loop to reduce systematic voltage mismatch

2.boost output impedance

boosting 存在代价:output range减小

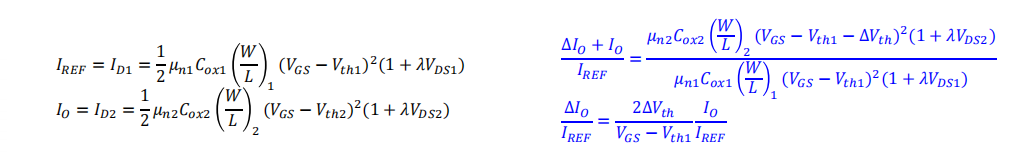

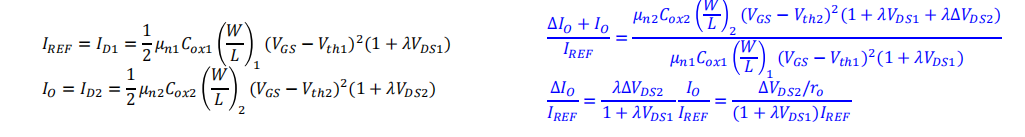

mismatch effects

1.(W/L) mismatch

影响

通过耦合等版图技巧减少该mismatch

2. mismatch

3. mismatch

4.fabrication factors

影响

high output impedance

可获得高output impedance,存在代价:

- output range problem

- voltage headroom problem

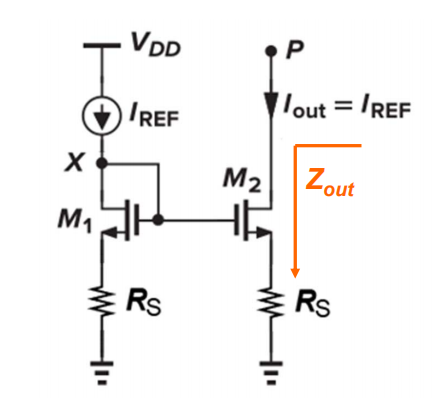

1. source degeneration current source

output voltage range problem

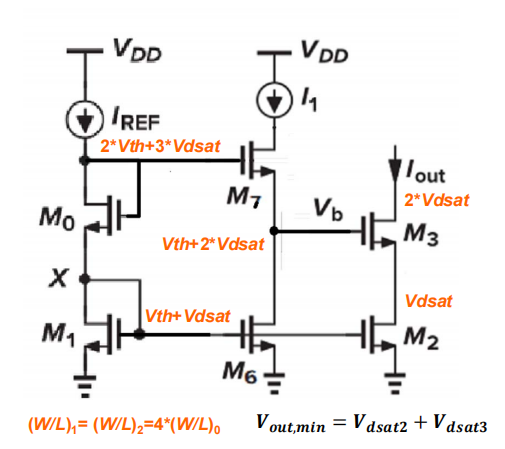

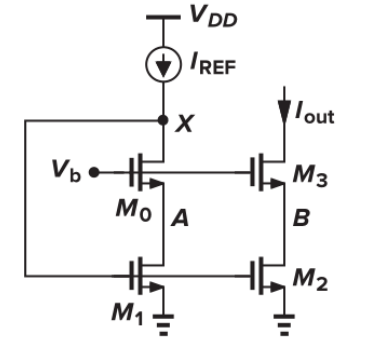

2.cascode current source

voltage headroom problem ( branch especially)

output voltage range problem

计算node voltage时除满足饱和区工作,还需注意电流大小限制

improved current mirrors

1.优化output range

实现的最佳output range

代价是恶化了voltage headroom problem&产生current systematic offset

为使:

,

只需

由于电流不变:将其W/L变为原先即可

代价1:的voltage headroom问题恶化()

代价2:电流copy产生systematic offset(管子的不同)

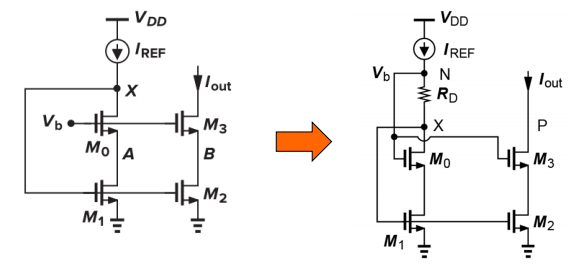

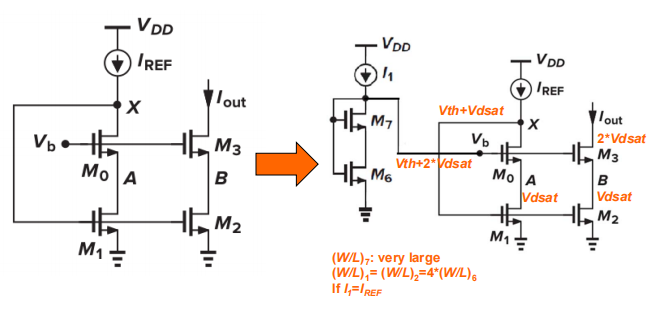

2.优化voltage headroom

high-swing cascode current mirrors, the best!!!

同时优化了output range和voltage headroom问题

由于要降低的电压,直接连接X node和

- : 优化voltage headroom problem

- : 优化output range problem

此时需要一个合理的使得MOSFETS均工作在saturation region即可

只需:

典型值:

1.电阻实现

只需合适的即可

but: PVT problem!!!

2.MOSFET实现

solve PVT problem!!!

代价:多一路电流,一般设置,并更改

利用极大的W/L可以使得一个MOSFET的,进而获得其的值:

已知的最小噪声偏置电流源:,即基于此想法

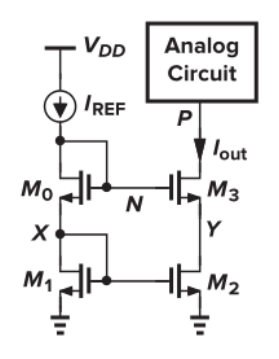

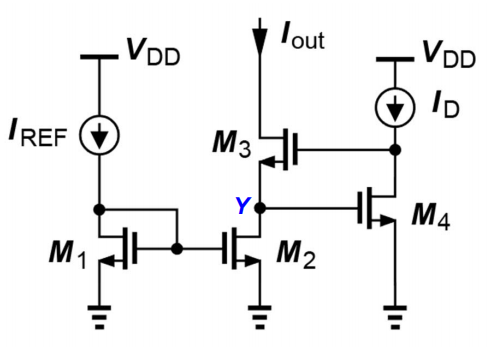

Boosting technique

本质:利用负反馈实现对某node电压的控制

当电流改变电压基本不变,实现高阻抗

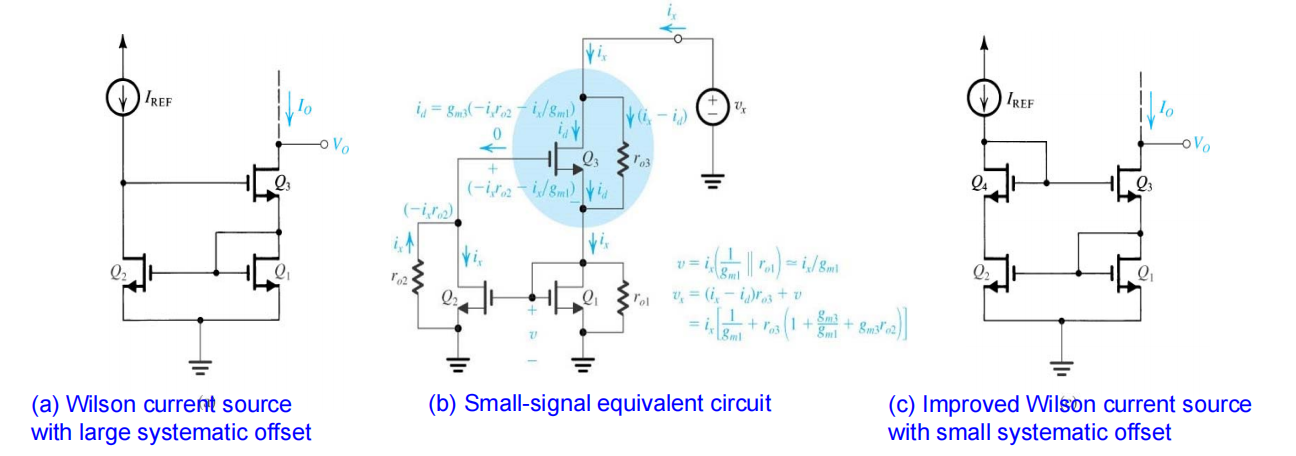

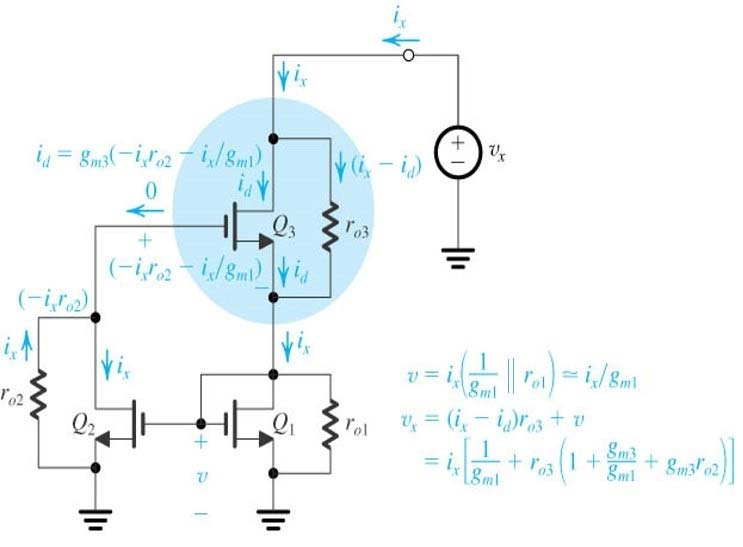

Wilson current source

和cascode current source几乎一致,唯一区别在于When branch is off: Wilson branch is off; Cascode branch is still on

但是cascode current source我们知道可以被改进!!!

图(b)分析:

-

当Q2不存在:普通current source,Q1作为的source degeneration

-

当Q2存在:source的电压变化以电流形式被copy,进而反馈到gate端,进而影响source电压,使得source电压被控制

-

从而等价于Q1的等效阻抗不再是,而是一个大阻抗

该node向下看的阻抗乘上Q2的

-

计算得约为 , boosted

-

进而, boosted

由于M4负反馈的控制,使得M2的等效source degeneration阻抗boost到, gain boost到

达到了double-Cascode的效果,代价是浪费了一点电流

Y作输入,M3作为CG的输出

node Y向上看等效阻抗除以M4的

原为, 等价M3的gm boosted

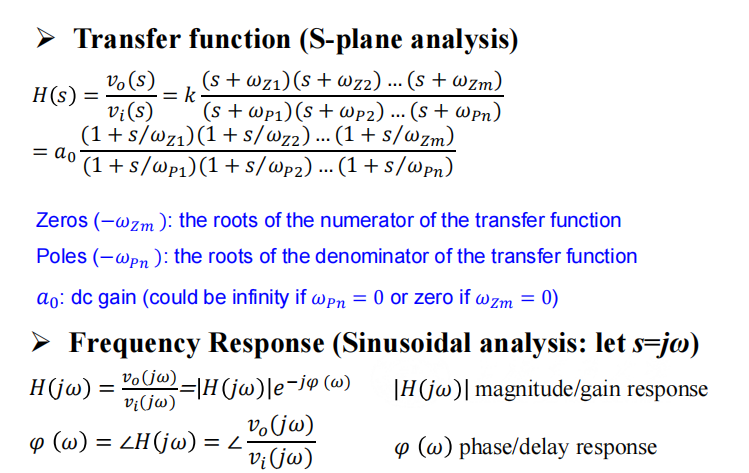

Frequency Response

basic concepts

-

线性系统(小信号电路)

-

稳态分析

magnitude/gain response & phase/delay response

-

S域分析:拉普拉斯变换

极点,零点

Bode Plot上零极点指极点的模,即

-

dB表示法:,定义-3 dB Frequency&Bandwidth:

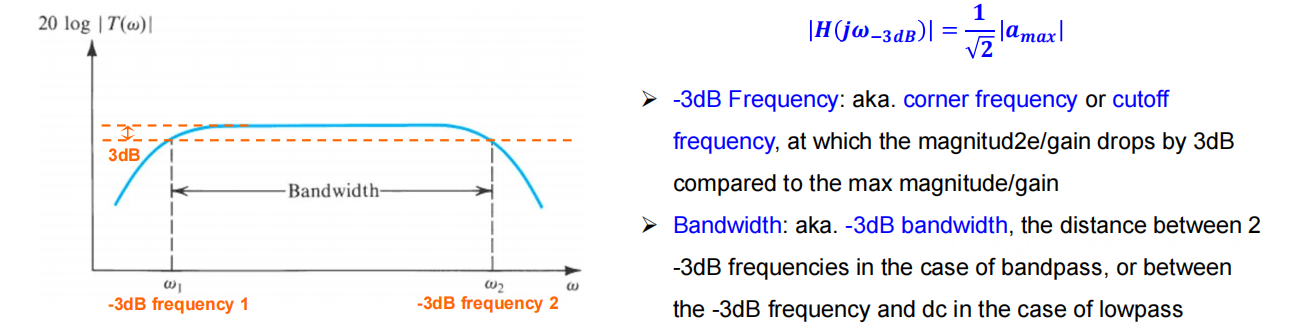

Bode Plot

一系列不精确的图表,大致画出并帮助分析电路的频率(相位、幅度)响应

近似前提:零极点都相互远离,互不影响

一般都成立

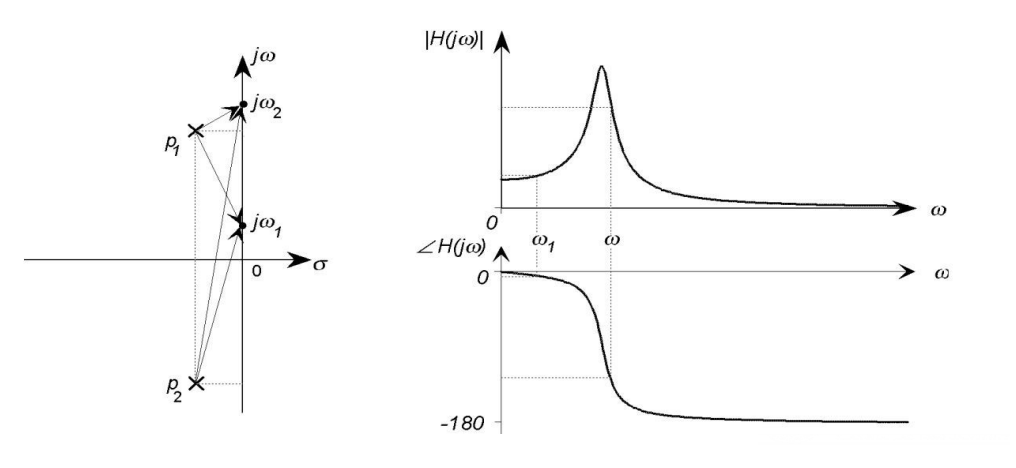

Bode Plot的零极点近似的本质是对Pole-Zero Diagram的近似:

实际上极点产生的存在数学上的一一对应:

但在模拟电路分析中基本是在附近,即Bode Plot中取零极点的模

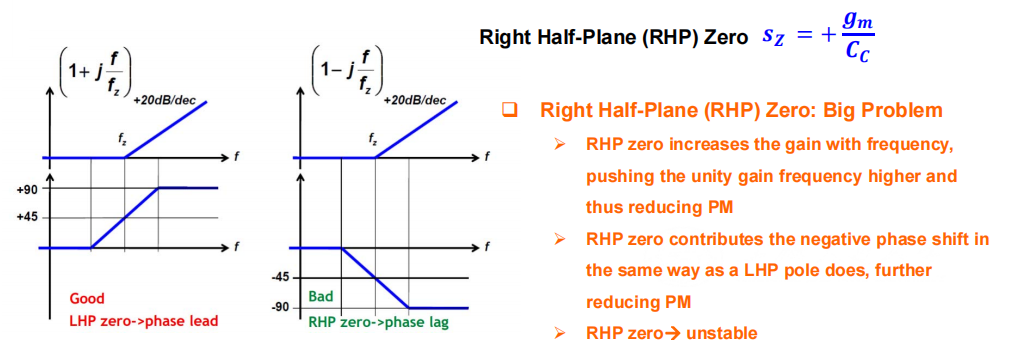

零极点对频率响应的影响和其所处平面有关、可以叠加

| 零极点种类 | 增益变化 | 相位变化 | 十倍频率外 | 备注 |

|---|---|---|---|---|

| 左极点 | -20db/dec | -45° | -90° | 减低gain&phase |

| 右极点 | -20db/dec | +45° | +90° | 系统必然不稳定 |

| 左零点 | +20db/dec | +45° | +90° | 提升gain&phase |

| 右零点 | +20db/dec | -45° | -90° | 提升gain、降低phase;系统较为可能不稳定 |

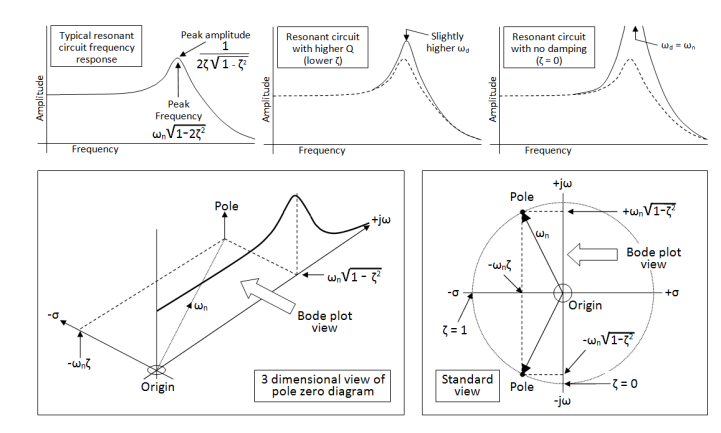

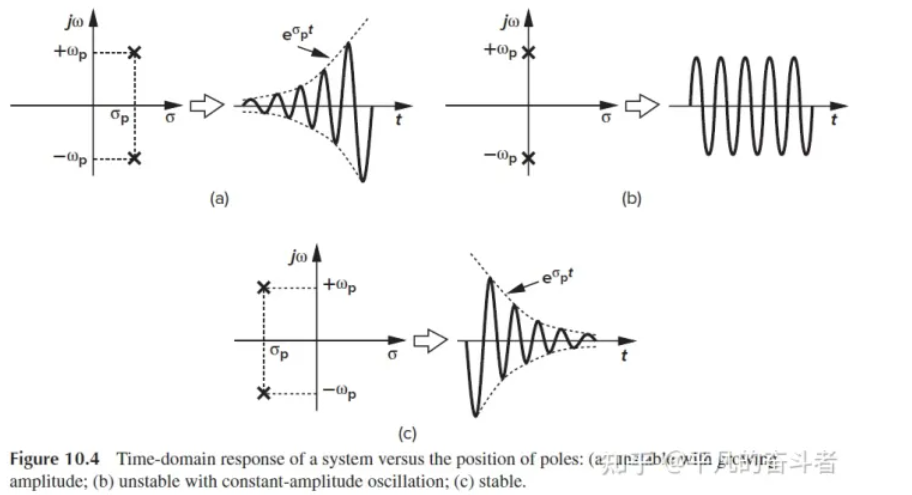

极点不同位置对系统稳定性影响(不稳定、等幅震荡、阻尼震荡稳定)

- 零点都是增大gain,极点都是减小gain

- 对phase影响需要看平面

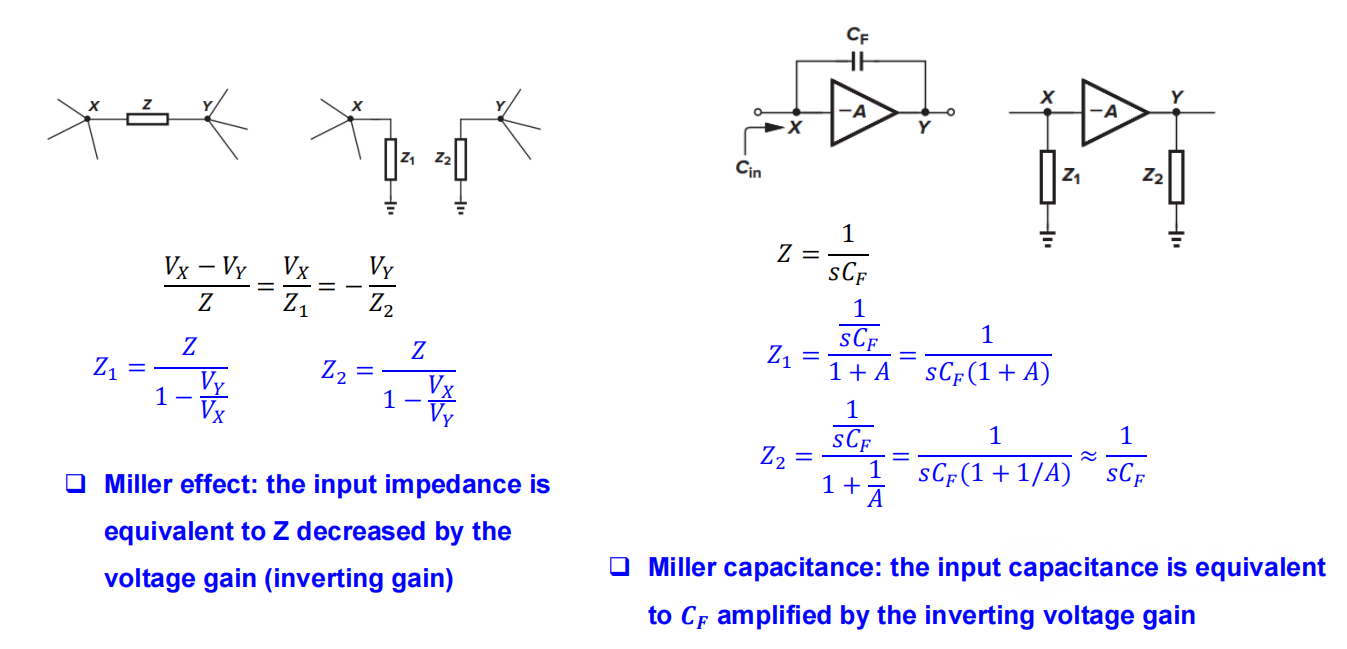

Miller Effect

跨接在输入和输出的阻抗可以等效为输入和输出各自对地的阻抗

一般是对电路参数不利的,较少电路可以利用Miller Effect

注意是任何阻抗,只是一般电容情况较多

gain为负数(-A)!!!

等效为输入端电容放大(1+A)倍,输出端电容约不放大

Miller Approximation for Pole Estimation

在分析电路频率响应的时候,将跨接的电容都分别等效到输入输出端

值得注意的是,高频率系统中Miller Effect可能会失效!!!

高频率时候若跨接的电容不是寄生产生的小电容,而是外接电容(如Miller 补偿电容),则近似于导线,此时会改变管子的连接方式,如形成类似diode connect的MOSFET,改变节点的输出阻抗和实际电容

这是一种不是特别准确的近似分析,但是会漏掉零点

一条feedback path会产生一个零点,但Miller Approximation打破了该path

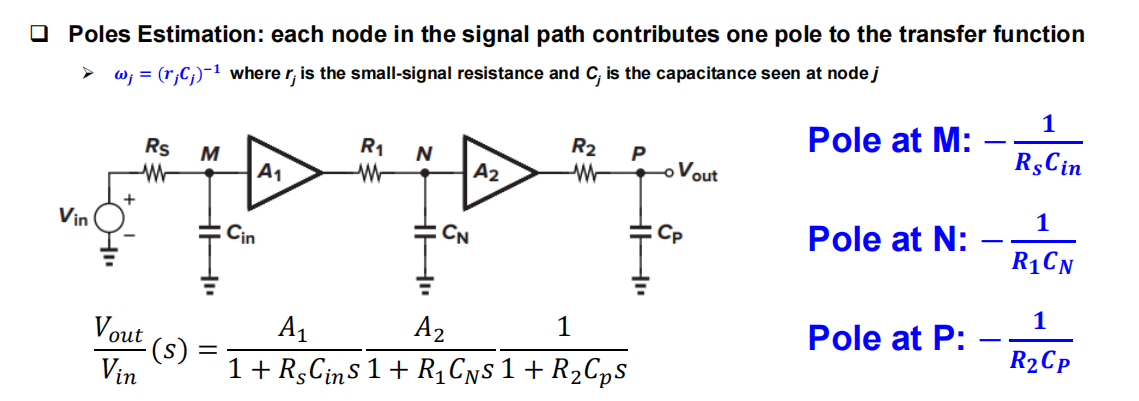

一个节点贡献一个pole,重点在于主次极点的判断

Major Poles Estimation Technique

-

判断出和small signal current path

-

在path上的每个节点:

- 用Miller Approximation等效其floating阻抗

- 估算其电容

-

计算看到的small-signal dc resistance ,判断其大小

Check: each high small-signal dc resistance node must have a negative feedback to define its dc bias voltage!!!

高阻抗意味着高增益,因此若没有负反馈电路,其直流偏置过于敏感

-

判断出major pole

最大的1~2个节点,它们决定了带宽 进而针对其改进

“ seen by ”:从电容两端看出去的等效对地电阻总和

“”:若Node j上电容非接地,需等效为对地电容

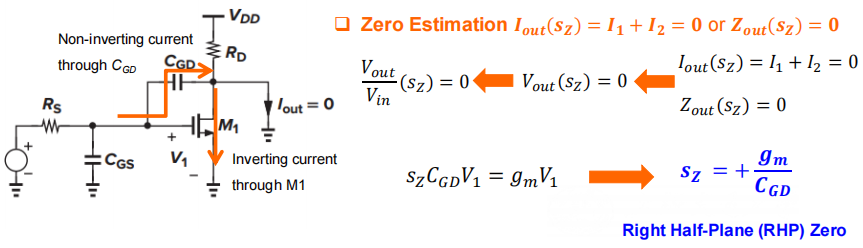

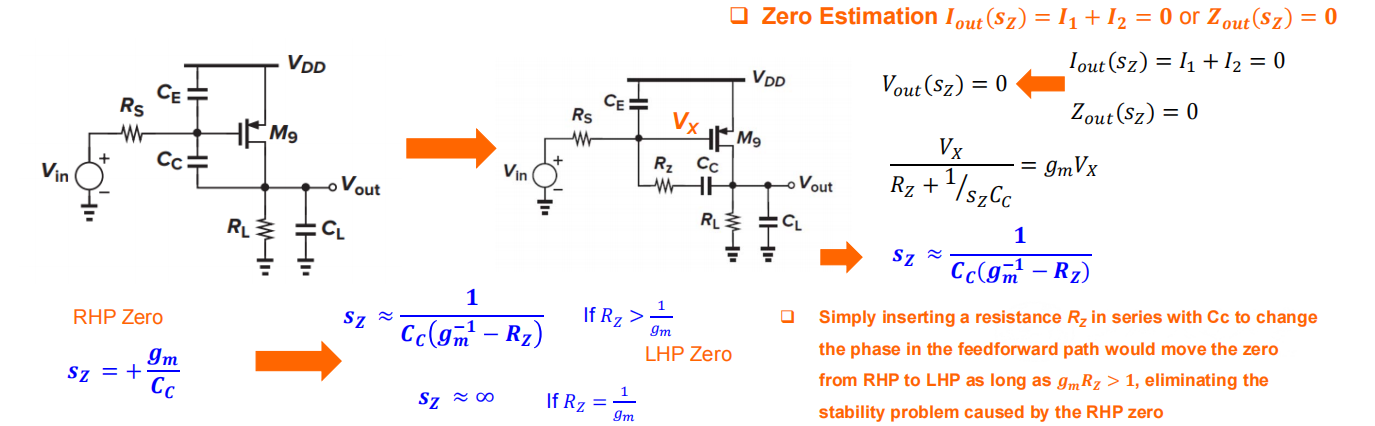

Zero Estimation Technique

每一条feedback通路必然会产生一个零点

因为是在复数平面上求解,两个电流值必然可以相同实现内循环:

改变两条signal path的phase会改变零点的位置(RHP or LHP)

Frequency Responses of Common Architectures

need to be completed

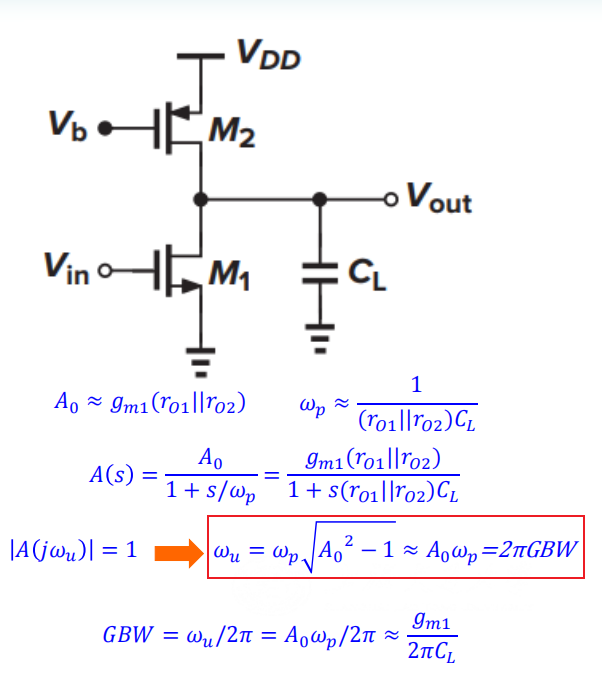

Gain-Bandwidth(GBW)

增益带宽积,一般是常数(即要做gain和bandwidth的trade off)

定义为

单极点系统中

,代入:

若引入反馈:,代入:

Opamps

高阻抗点的电压偏置一定要在close loop中用负反馈定义,不然其电压会因为极大gain而极为敏感,从而受到PVT影响

PSRR

实际中,Vdd相对于Ground一般是很dirty的,存在许多noise

用PSRR表征运放的power supply rejection

,dB form:

注意Vdd到output可能有多个small signal path

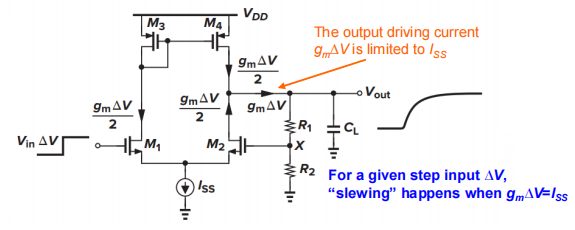

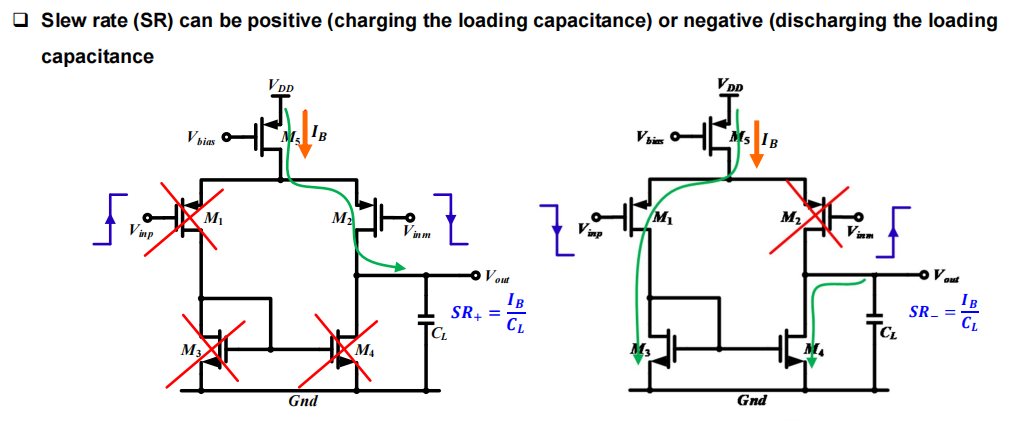

Slew Rate

实际输出负载一般是容性,用Slew Rate表征Opamp对其的充放电速度

Slewing现象:由于受制于输出电流的最大值,即若输出理想充放电电流值大于可提供的最大值,输出电流由指数退化到线性

,

此时出现失真(independent of input)!!

一个例子,当输入:

One-Stage Opamp

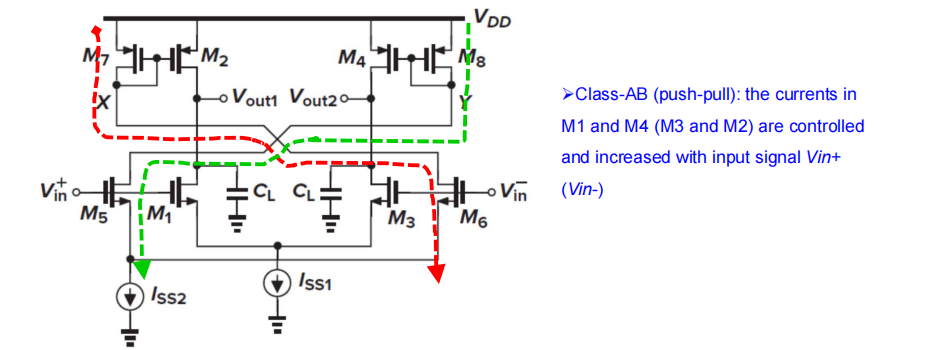

Differential Pair

即之前所学diff pair with active load

Slew rate最大为

-

提高电流大小,用功耗交换

-

Class—AB(push-pull),根据输入信号大小调整电流大小

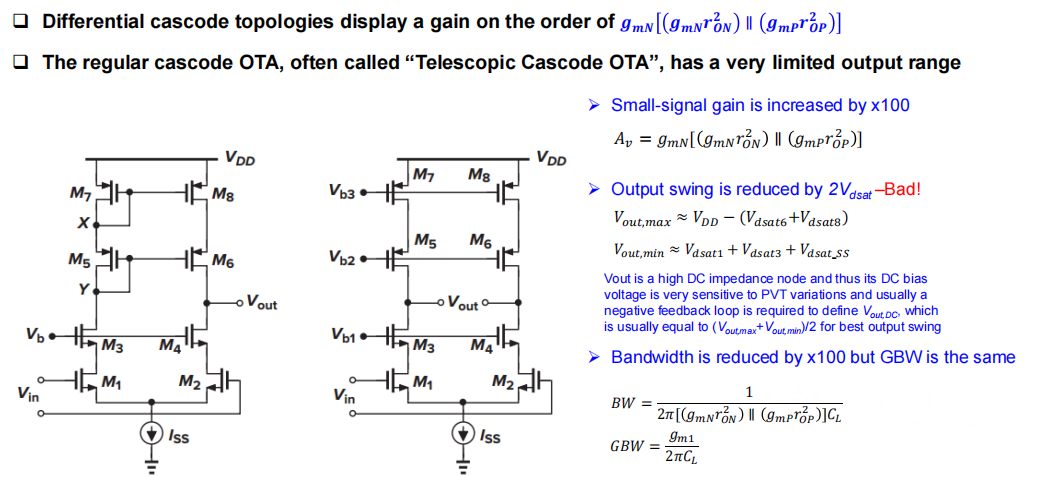

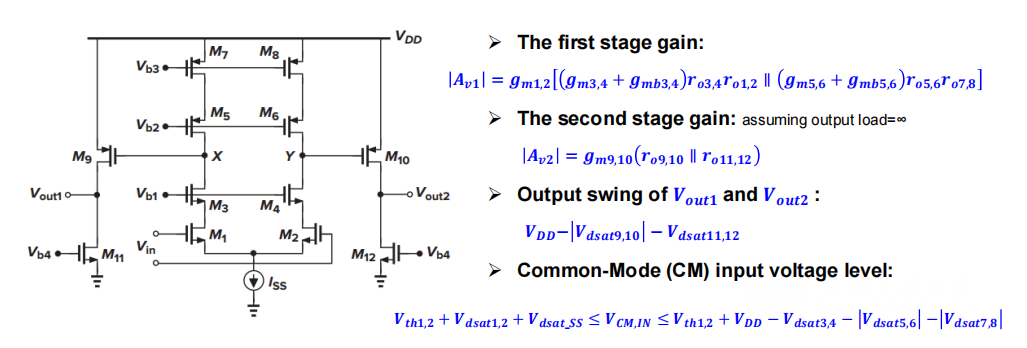

Cascode

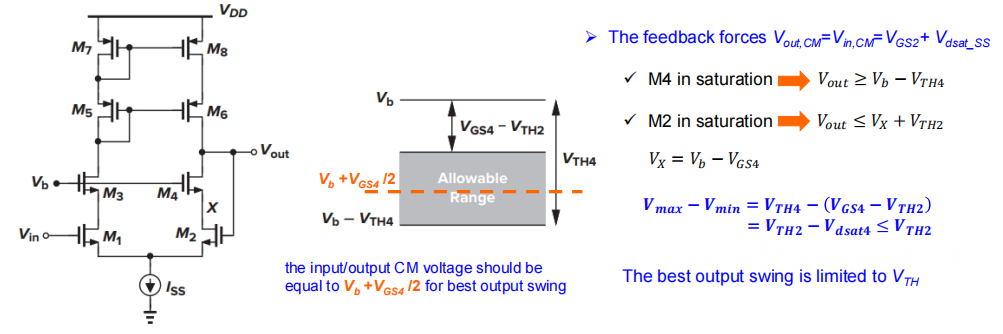

diff pair中采用cascode架构,进而获得更高的gain&

代价是会产生voltage headroom problem

若进一步考虑到output node高阻抗,需在close loop中用负反馈定义其偏置电压:

受限于输入共模,输出共模受限于,负反馈导致输入和输出共模需要一样(或存在某种关联),进一步限制了输入共模,恶化其headroom problem

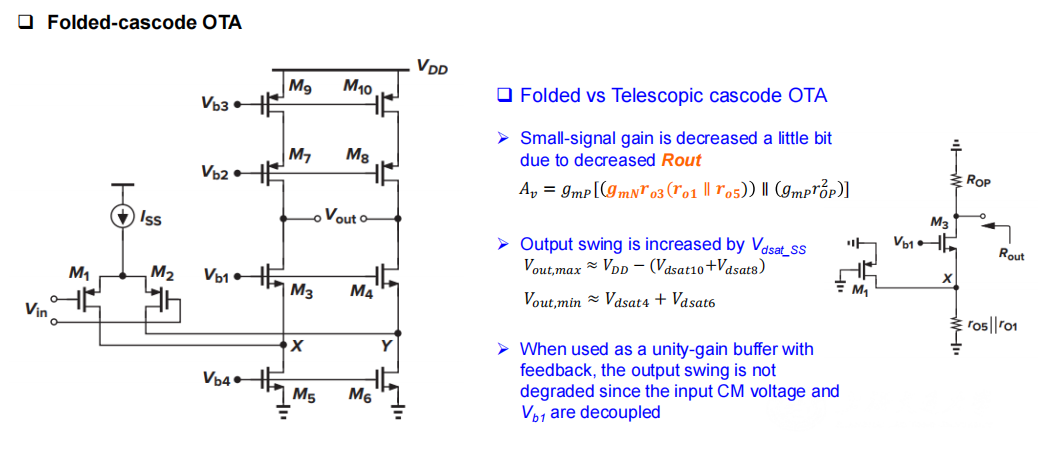

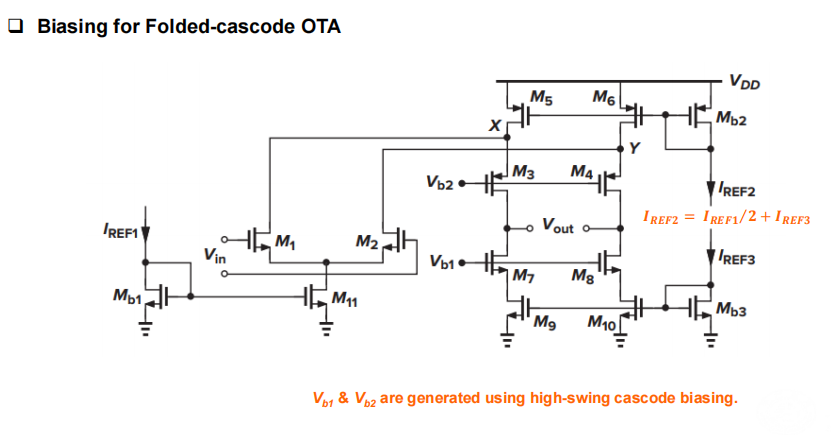

Folded-Cascode

分离Vb1和Vin,缓和上述problem

代价是extra current和需要极为精确的偏置

电流存在约束:

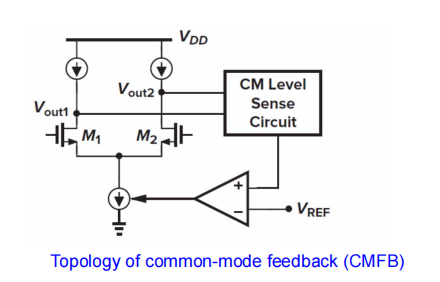

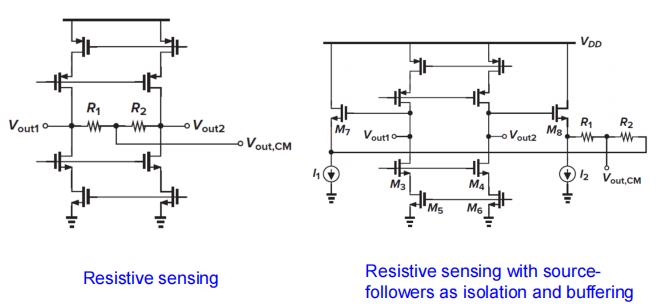

CMFB

讨论一般fully-differential opamp中的common mode feed back

计算出common mode output voltage比较

直接用电阻会影响gain,因为被电阻减小,一般用Source Follower把 copy出来再算均值:

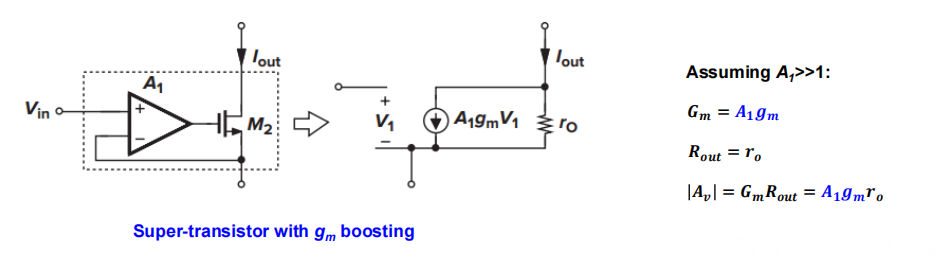

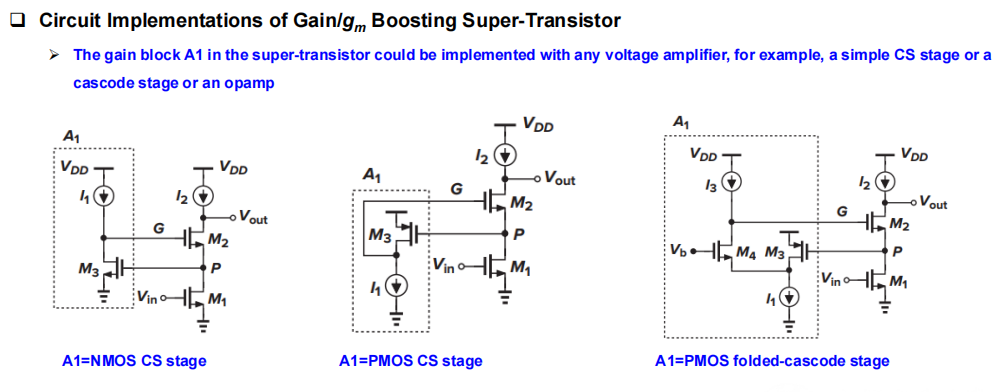

super-transistor

本质是gm boosting

用单个管子+负反馈形成类似cascode的效果但无voltage headroom problem

实现:

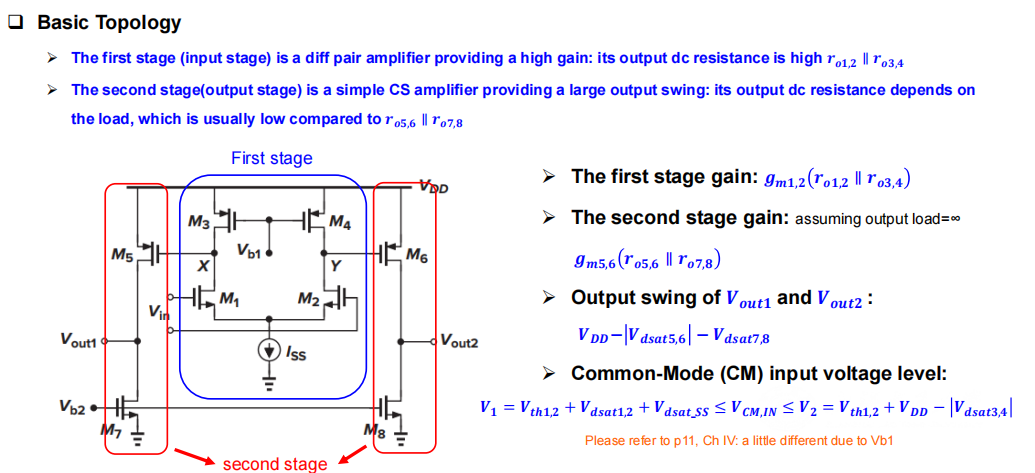

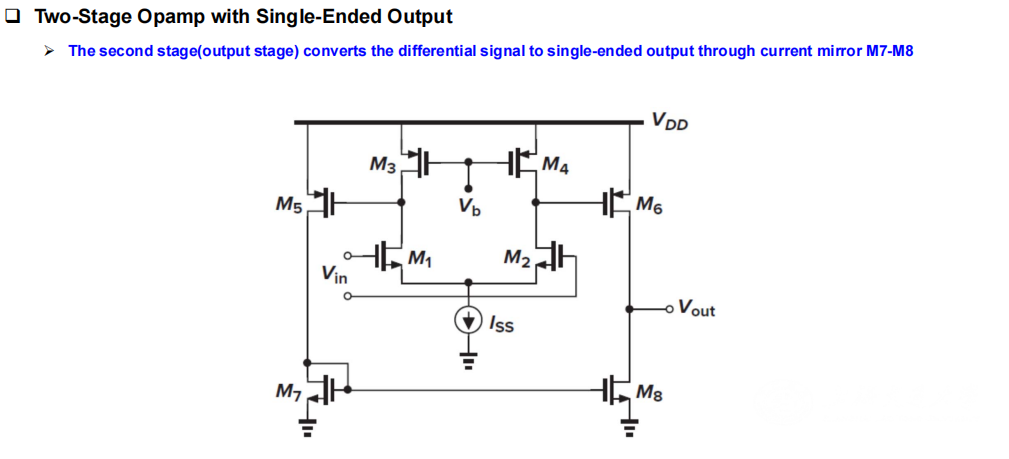

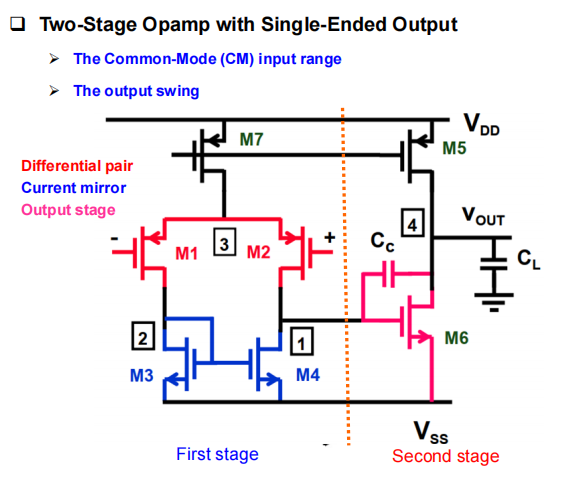

Two-Stage Opamp

同时获得高增益和高swing

第一级:high gain&low swing

第二级:low gain&high swing

代价是一级运放至少多产生一个pole,会存在稳定性问题

所以一般两级,用Miller电容补偿

其中第一级可以用任何所需one-stage opamp代替

如cascode:

也可以用单端输出:

电容就是Miller电容,用作相关补偿

Stability&Frequency Compensation

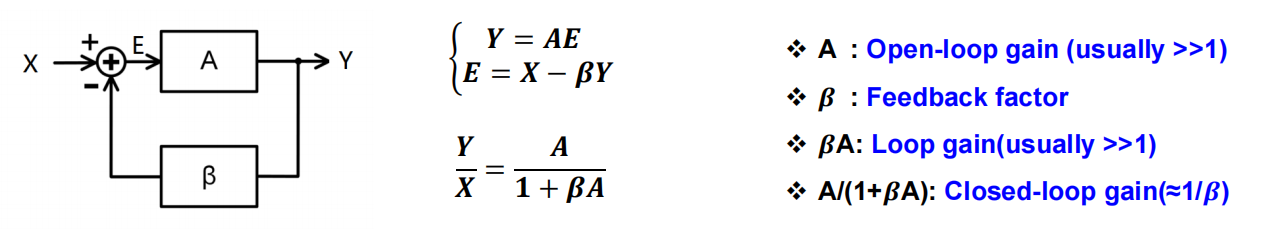

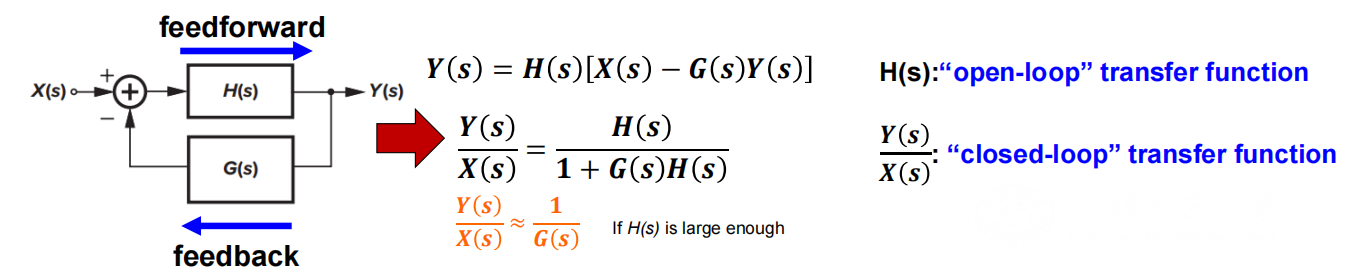

Negative Feedback

Loop gain:

s域分析:

1.Gain Desensitization

牺牲gain,换取系统的predictable,减少PVT影响(无源元件、比值)

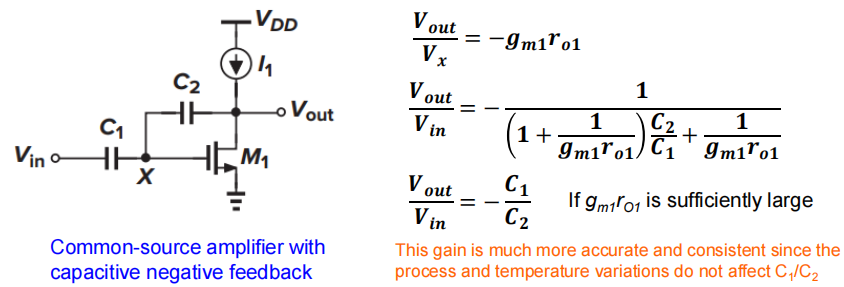

例如:引入C1、C2,将CS amplifier gain从转为

2.Bandwidth Extension

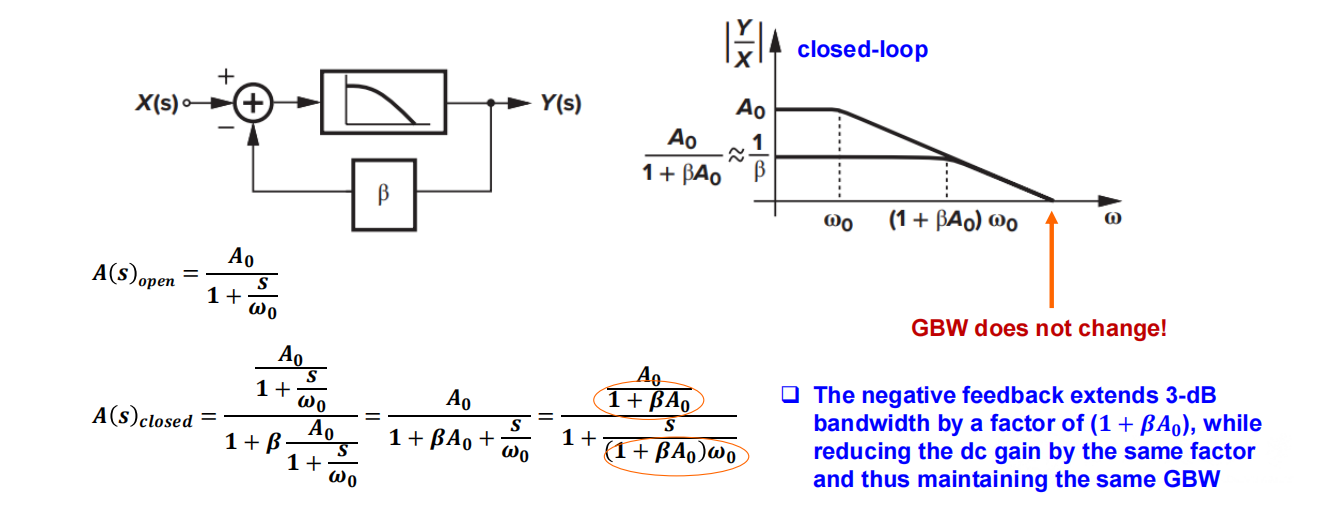

a single-pole system为例(其余原理类似):

- DC gain降低为

- new pole:,带宽增加

- GBW几乎不变

3.Linearity Improvement

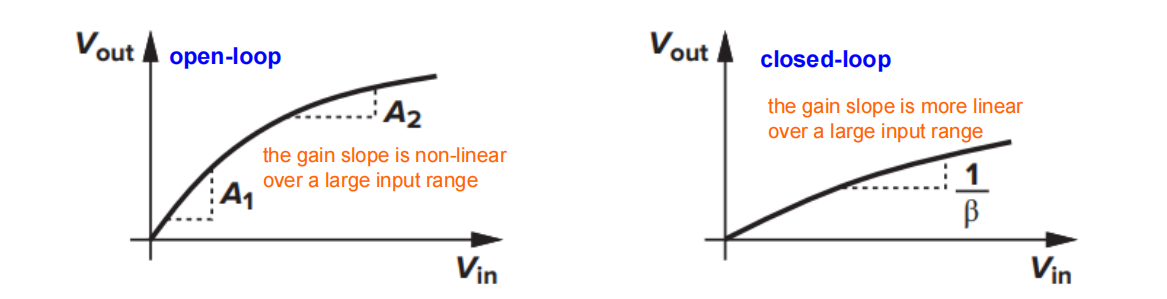

open loop:

closed loop:

-

相对open loop减小,即线性度提升

-

若给定误差限制:input range 提升

Stability Analysis

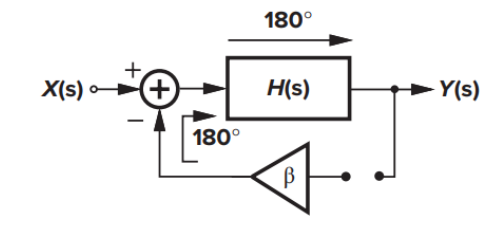

负反馈的存在可能会导致系统产生正反馈,继而引发稳定性问题

Barkhausen’s Criteria

震荡的必要条件,但不是充分的

目前还没有一个既是充分条件也是必要条件的简单振荡准则

当的相位达到-180°& loop gain$\geq$1时,系统不稳定,等号处系统等谐震荡

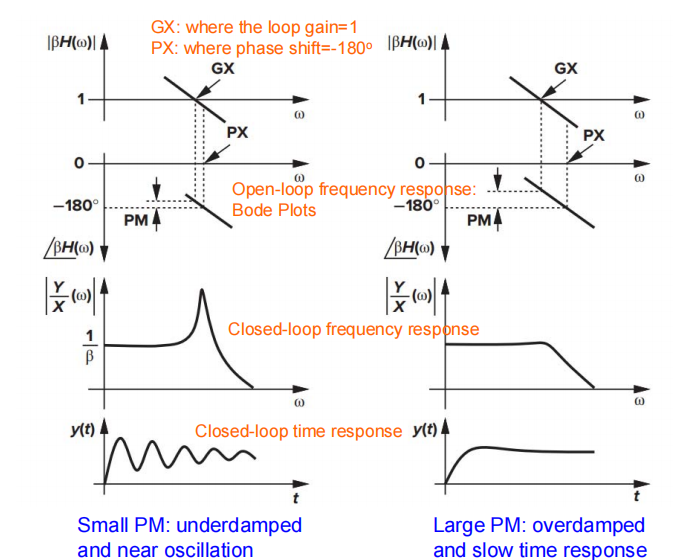

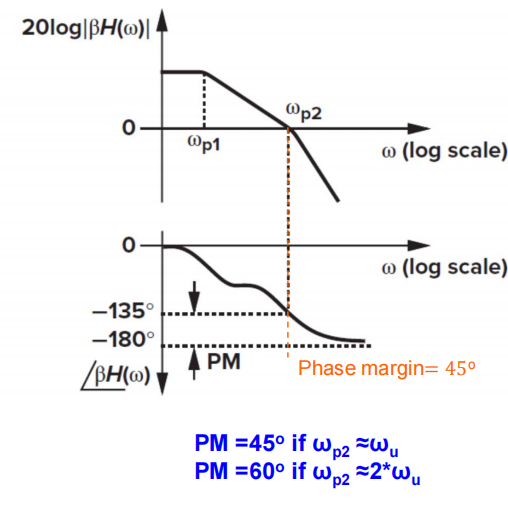

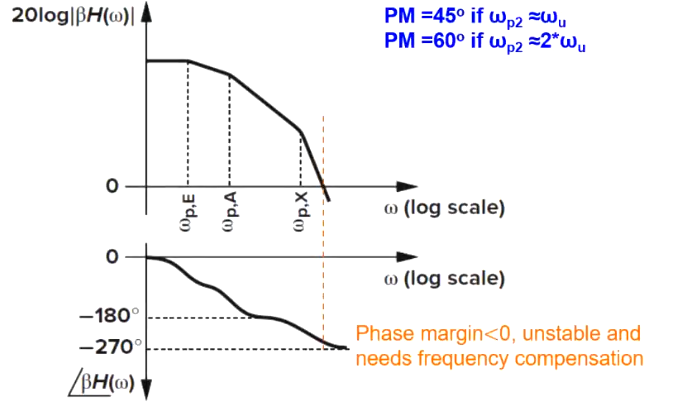

Phase Margin

PM=∠,其中

运用Bode Plots可以简便快速地判断系统稳定性

利用open loop的的bode plots估算close loop的频率响应

- PM较小时会close loop的frequency response会在产生一个尖峰,且系统的time response接近震荡现象

- PM较大无上述情况,但time response较慢

- 论文证明:PM在60~70°最佳

值得指出:single- pole system无条件稳定,因为至多产生-90°的phase shift,不会到达-180°,PM$\ge$90°

- 可以把第二个极点移远,实现PM即系统稳定性的改善

- 如果同时存在负反馈和正反馈,但负反馈为主,系统仍然稳定

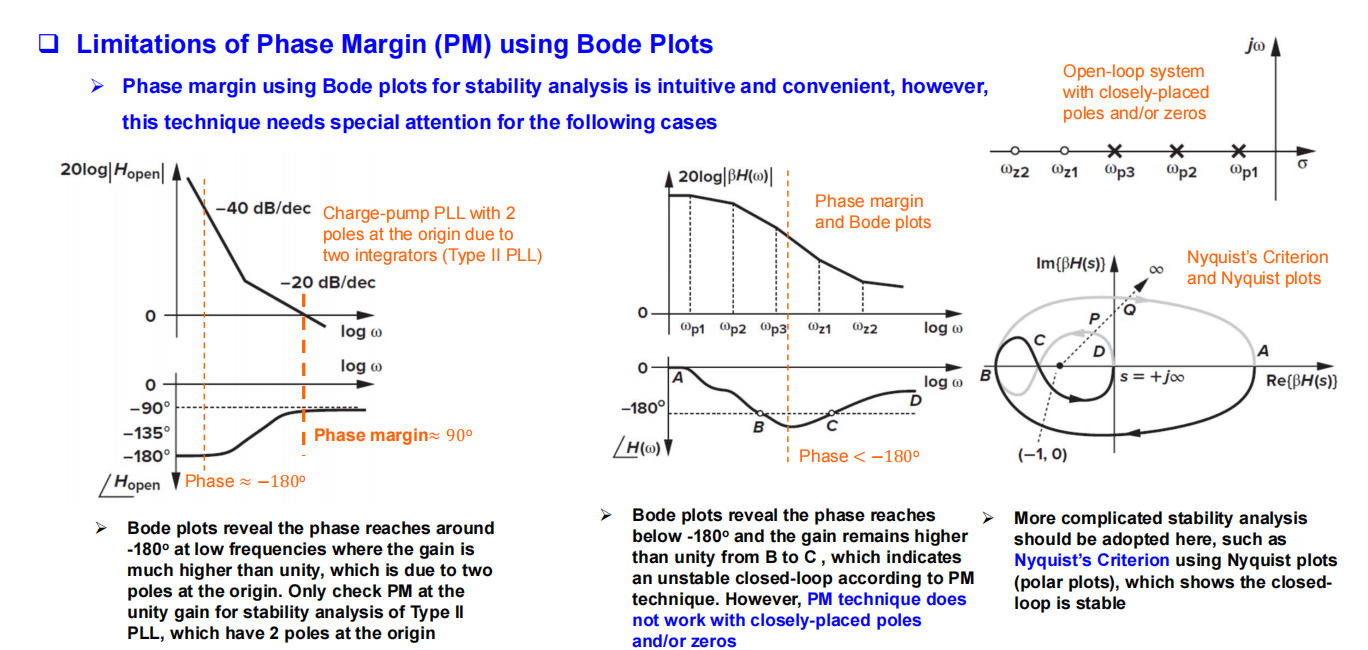

Limitations&Special Cases

Barkhausen’s Criteria & Bode plots 存在应用限制

bode plots基于Barkhausen’s Criteria,存在诸多假设(如零极点要求相差很远、s=jw近似等)

进阶版:Nyquist’s Criterion & Nyquist Plot

即在s plane分析,而不是用取模的近似分析

Case1

CPPLL的Bode Plot从-180°开始(两个极点在原点),之后又一个零点,高频PM=90°但低频PM=0°,是否不稳定?实际上稳定!

Case2

Bode Plot phase中间小于-180°但经过零点后返回

中间部分是否不稳定?实际上可以稳定!

Bode Plot中存在密集的零极点,Bode Plot中零极点相互远离的假设失效!

建议改进设计,使得零极点相互远离

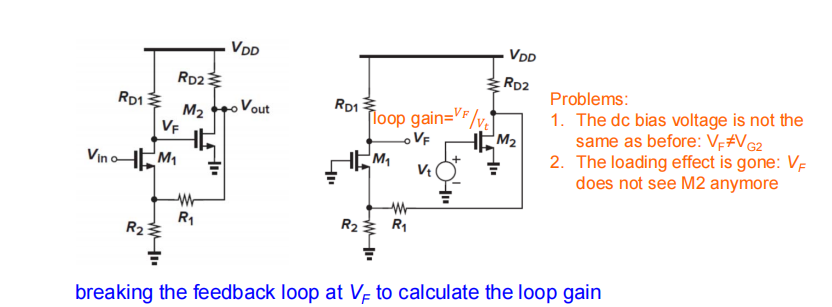

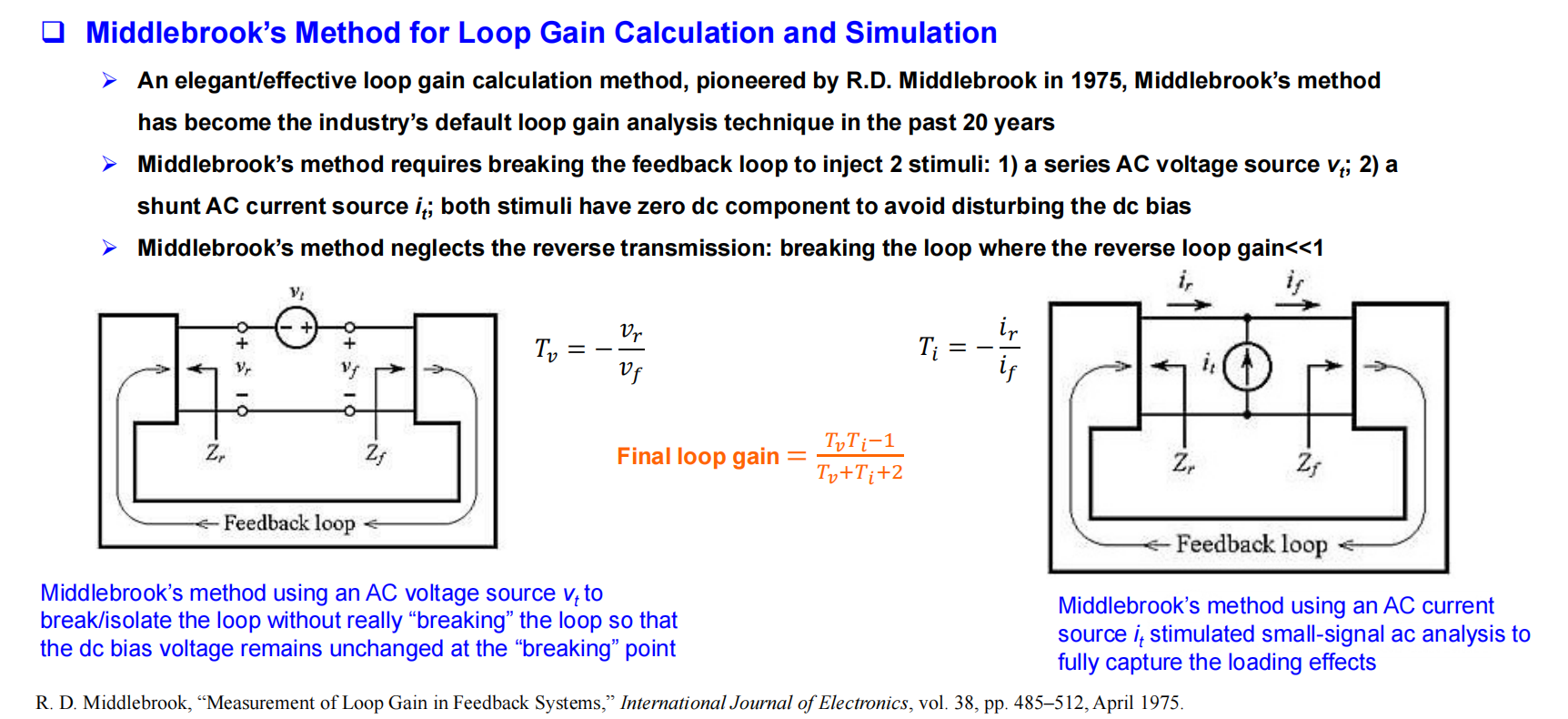

Middlebrook’s Method

Bode plot是针对open loop的loop gain的,实际电路往往是close loop的,我们如何得到其open loop的loop gain?

实际应用时候,已经存在反馈环路,需手动break loop,得开环的loop gain

break loop ask for:

-

如何维持dc bias voltage?

-

如何维持loading effects?

-

multi loop或nested loop 如何 break?

设计中尽量避免

值得指出:: a weak unstable loop is allowed if there is a strong stable loop to overcome its effect

常见的计算Loop gain: break loop and calculate

- DC bias 难以维持,原本

- 原本M2上的gate寄生电容会load M1

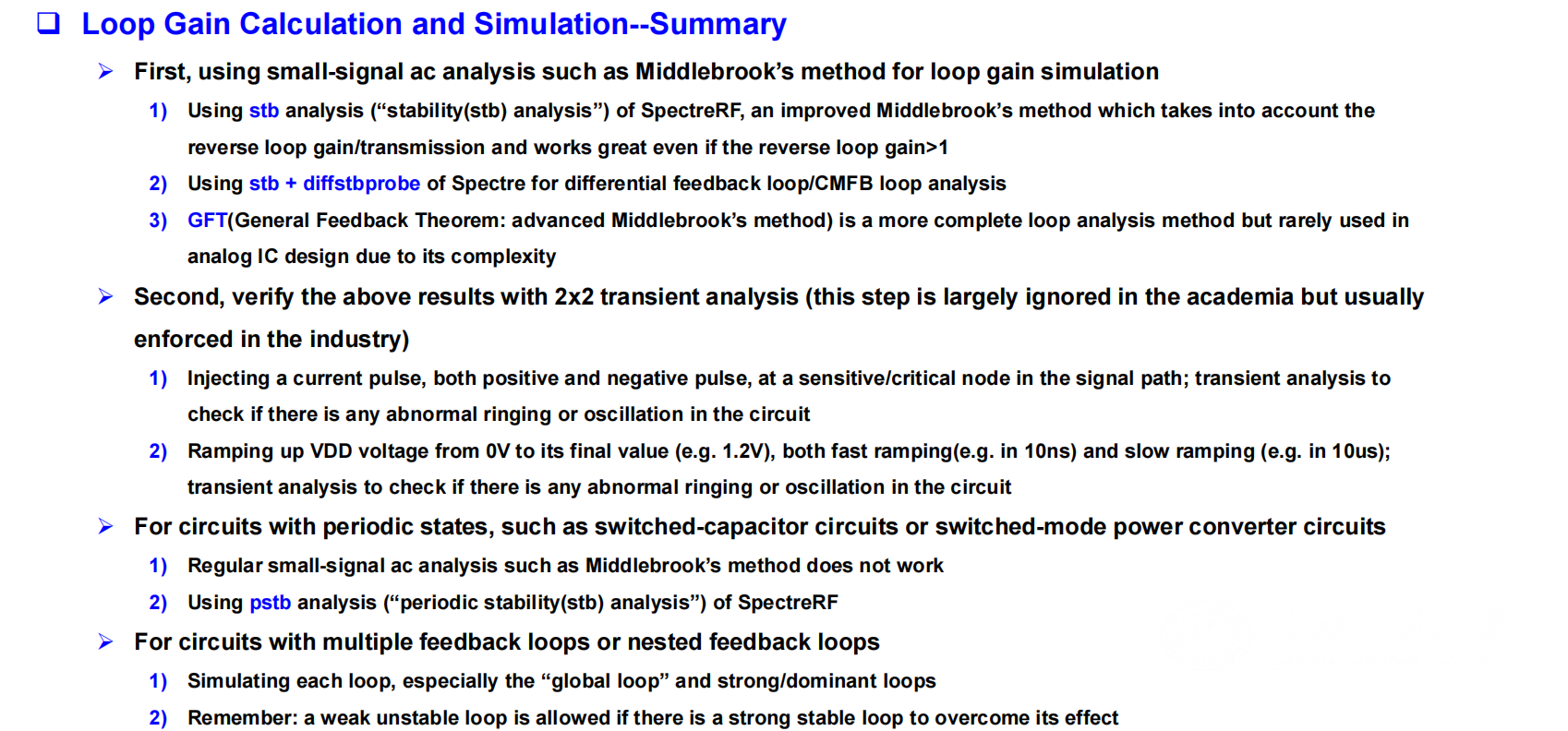

Solution: Middlebrook’s Method

现代工业界改进:

- First: stb仿真(改进版Middlebrook),但是可能对nested loop不够准确

- Second: 时域验证

- 周期性小信号分析需采用 pstb仿真

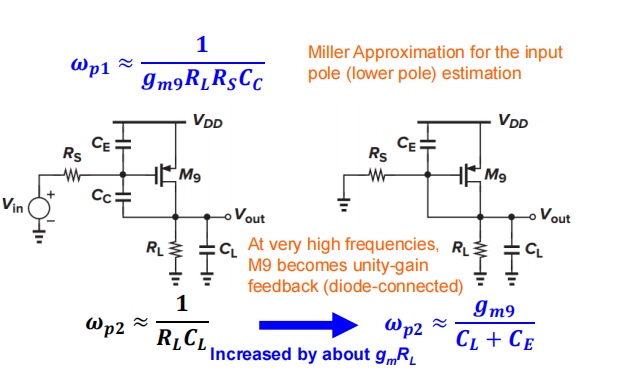

Frequency Compensation

- 第一级极点内推

- 第二级极点外推

本质:move lower than the pole,逼近single pole system

for example: to get 60° PM

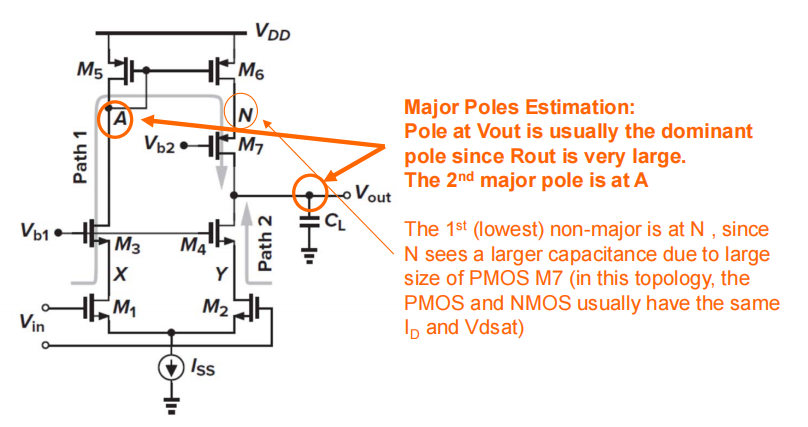

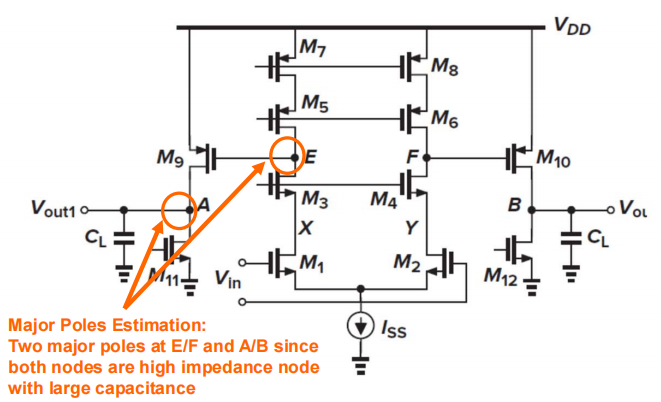

应用 Major Pole Estimation Technique快速判断主次极点

Dominant Pole Compensation

向内推主极点(一般是输出处,若无 Miller补偿等)

增大主极点处的电容,使得

增加并没有用处:dc gain同时增加,不减少

one-stage

| Node | 电阻 | 电容 | |

|---|---|---|---|

| out | 特大() | 特大() | 主极点 |

| A | 小(1/gm) | 大() | 次极点 |

| N | 小(1/gm) | 小 | 非主要极点 |

two-stage

| Node | 电阻 | 电容 | |

|---|---|---|---|

| E(第一级输出) | 特大() | 一般 | 主极点 |

| A(第二级输出) | 大() | 一般 | 次极点 |

| X&Y | 小(1/gm) | 一般 | 非主要极点 |

实际上 由于大电阻电容的存在已经较小,若仍然采用dominant pole compensation,需要在E处加极大电容,同时导致GBW极小()

采用Miller Compensation,通过Miller Effect给E处加大电容

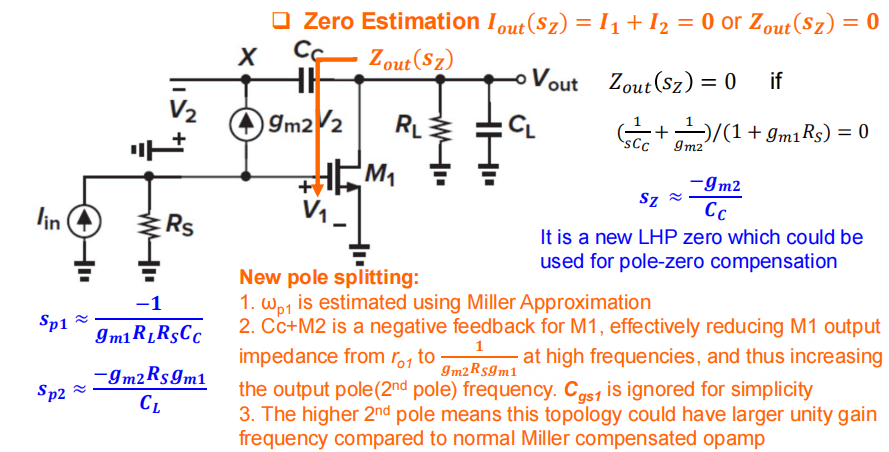

Miller Compensation

pole splitting

-

增大dominant pole电容,内推第一极点

-

同时外推第二极点

高频下跨接的Miller电容近似导线,降低R、略增大C

另一种角度:feedback path,使得第二级输出电阻有效降低

电阻调零

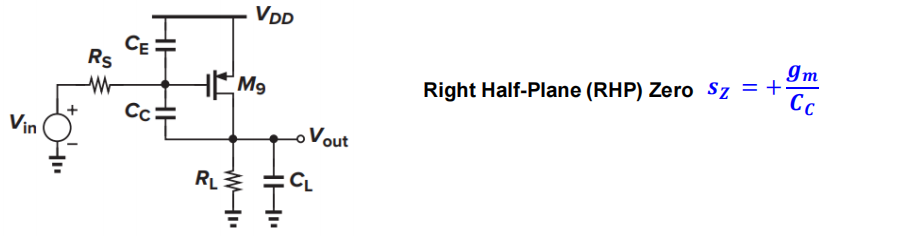

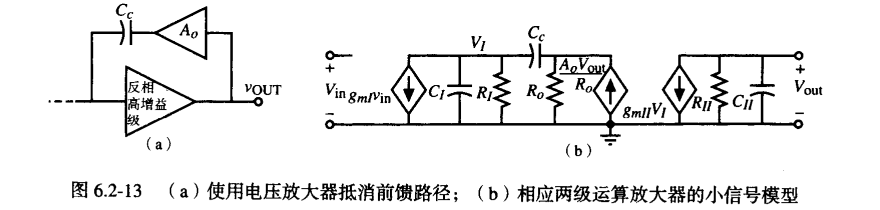

但由于电容feedforward signal path的引入:产生RHP zero,bad!

-

-

的feedforward path(前馈支路)

某个复频率电流相加为0:形成Zero

改变两条signal path的phase会改变零点的位置(RHP or LHP)

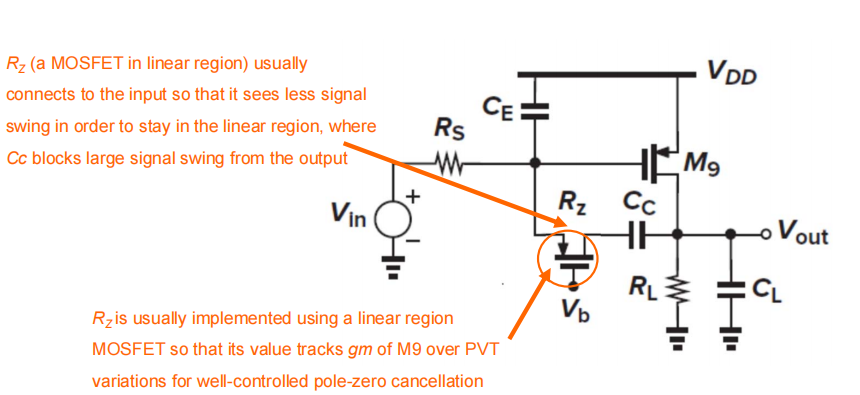

加调零电阻,使得零点位于LHP

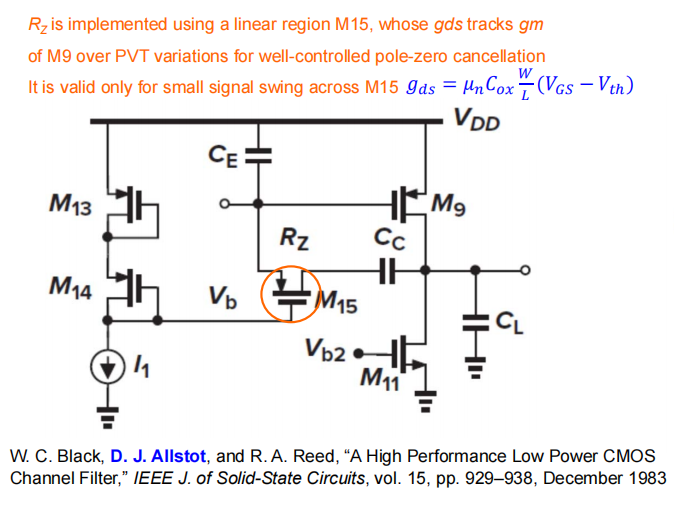

可以用Linear region的MOSFET代替电阻R,实现抗PVT

但MOSFET要放在侧而非侧,因为左边为输入,信号swing较小,容易保持在linear region;右侧为输出,信号swing较大,不容易保持在linear region

Pole-Zero Cancellation

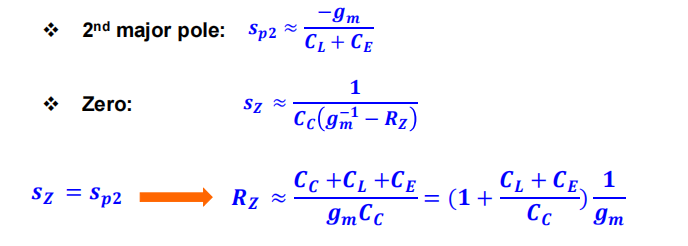

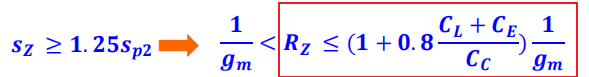

用上述LHP的零点抵消,形成single pole system

PVT&近似公式,难以完全抵消:产生临近的零极点,doublet!!!

经验公式:

将zero和p2接近但不完全重合,避免doublet同时改进PM

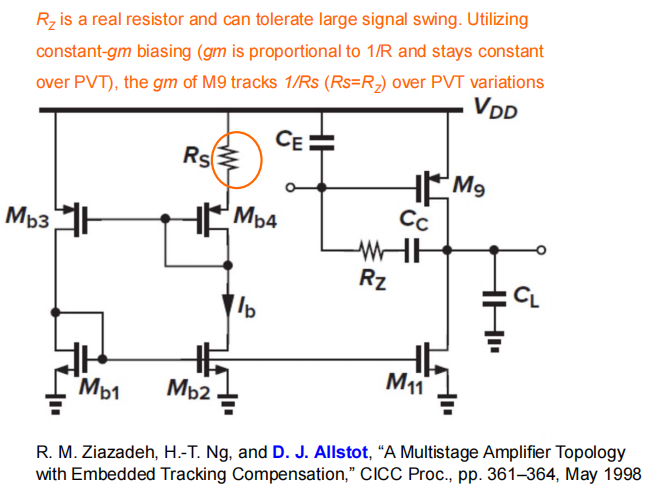

gm-tracking

两个想法,实现的tracking

本质是让,使得不变

-

匹配

-

匹配

-

匹配,一个current copier(未必1:1)

当PVT引起上的电流变化,其电流变化同样发生在左边的偏置电路,影响压降

左侧为constant-gm电流源,,直接用于bias,使得 track

break feedforward path

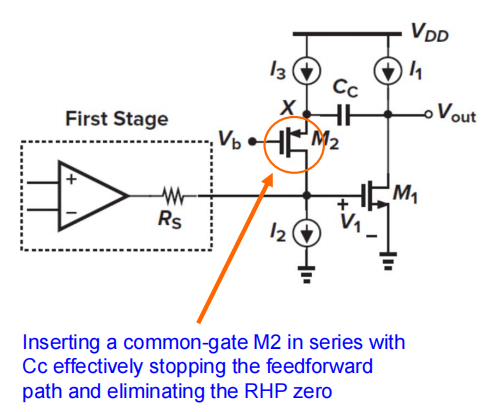

利用Common Gate P-MOSFET的隔离作用,抵消前馈通路,实现单向的信号通路,不引入RHP Zero

- feed back path 通畅:看到,低阻抗

- feed forward path 断开:看到,高阻抗

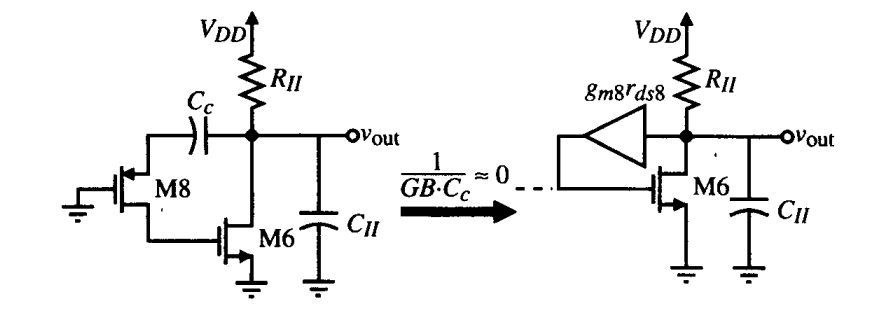

同时由于CG存在的增益,在高频下等效于一个diode connected的MOSFET加上一个增益,使得负反馈进一步加强,第二级输出电阻进一步下降,进一步外推

类似gm boosting

同时形成新的LHP Zero,可以用作pole-zero cancellation:

单信号通路,用估算Zero

第一极点仍然通过Miller内推,不变!

第二极点甚至被推的更远,good!

| 电阻调零 | CG隔离 |

|---|---|